當(dāng)前的技術(shù)瓶頸

對(duì)于大多數(shù)基于PC運(yùn)行的數(shù)字化儀和數(shù)據(jù)采集系統(tǒng)來說,,常見的問題是由于模數(shù)轉(zhuǎn)換器技術(shù)領(lǐng)先于PC總線技術(shù)而引起的。當(dāng)高速,、高分辨率的數(shù)字化儀產(chǎn)品將大量的模擬信號(hào)轉(zhuǎn)為數(shù)字信號(hào)時(shí),,PC卻無法對(duì)這些數(shù)據(jù)進(jìn)行完整的讀取和處理,這時(shí)就產(chǎn)生了瓶頸效應(yīng),。譬如,,基于USB的數(shù)字化儀通常采用高于100MS/s的采樣率,而數(shù)據(jù)傳輸至PC的速度往往受總線限制而局限于每秒幾兆字節(jié)(MS/s),。這種瓶頸效應(yīng)導(dǎo)致數(shù)字化儀不得不暫停數(shù)據(jù)采集,。在等待清空此前儲(chǔ)存信息的同時(shí),一些重要的事件往往容易被遺漏,。而且,,緩慢的傳輸速度限制了系統(tǒng)的整體測(cè)量和分析速度。因此,,很多需要進(jìn)行大量數(shù)據(jù)采集,、儲(chǔ)存和分析的應(yīng)用往往將此問題視為重中之重。

解決方案

解決此類瓶頸的一個(gè)方法是將數(shù)據(jù)傳送至板上現(xiàn)場(chǎng)可編程門列陣(FPGA),使終端用戶可以處理數(shù)據(jù)并嘗試減少需要通過總線向PC傳輸?shù)臄?shù)據(jù)總量,。但是,,當(dāng)進(jìn)行高速數(shù)據(jù)傳輸時(shí),,這種方法就變得相當(dāng)昂貴了。因?yàn)樗枰叱杀镜腇PGA固件開發(fā)工具和專業(yè)的工程知識(shí),。開發(fā)高級(jí)FPGA固件難度較高,,它依賴于一些算法的實(shí)現(xiàn),而且固件的設(shè)計(jì),、調(diào)試及運(yùn)行都需要花費(fèi)大量的時(shí)間,。通常只有大型項(xiàng)目才會(huì)給予如此巨大的投資。

德國Spectrum儀器為數(shù)字化儀用戶提供了更為簡(jiǎn)便和高效的解決方案,。該方法融合了新的PC總線技術(shù)與工廠工程FPGA程序及一系列智能數(shù)據(jù)采集和傳輸模式,。其結(jié)果能夠幫助用戶輕松的優(yōu)化數(shù)據(jù)傳輸過程,進(jìn)行更復(fù)雜的測(cè)量并分析在PC環(huán)境中運(yùn)行的各種程序,。一旦如此,,諸如MathWorks公司的MATLAB,NI公司的LabVIEW或是德國Spectrum公司的SBench 6這些現(xiàn)成的軟件工具都將被用以處理輸入數(shù)據(jù),。這種方法減少了對(duì)定制化固件的需求,,并因簡(jiǎn)化項(xiàng)目開發(fā)進(jìn)程而顯著降低工程造價(jià)。

圖表1顯示了一些數(shù)字化儀的接口和標(biāo)準(zhǔn)的數(shù)據(jù)傳輸速度,,這些速度適用于延長的采集周期,。如表所示,如果板上ADC的數(shù)字化維持在10-200MS/s的范圍甚至更高,,內(nèi)嵌于USB或PCI這類較慢或老式的總線系統(tǒng)的數(shù)字化儀更容易遇到數(shù)據(jù)傳輸?shù)钠款i,。如果使用多通道的數(shù)字化儀,問題會(huì)更加嚴(yán)重,,因?yàn)閿?shù)據(jù)的采集率將隨通道的增加而加倍,。

|

總線類型

|

標(biāo)準(zhǔn)的可持續(xù)數(shù)據(jù)傳輸速度

|

|

USB 2.0

|

<35 MB/s

|

|

Gbit Ethernet/LXI

|

<70 MB/s

|

|

PCI/PXI/cPCI

|

< 100 MB/s

|

|

PCI-X 66 MHz

|

< 240 MB/s

|

|

PCIe/PXIe x1 lane Gen1

|

< 170 MB/s

|

|

AXIe (PCIe based backplane)

|

< 1.5 GB/s

|

|

PCIe x8 lane Gen2

|

< 3.4 GB/s

|

表1 顯示常見數(shù)字化儀總線類型及其標(biāo)準(zhǔn)數(shù)據(jù)傳輸速度

真正的高速總線

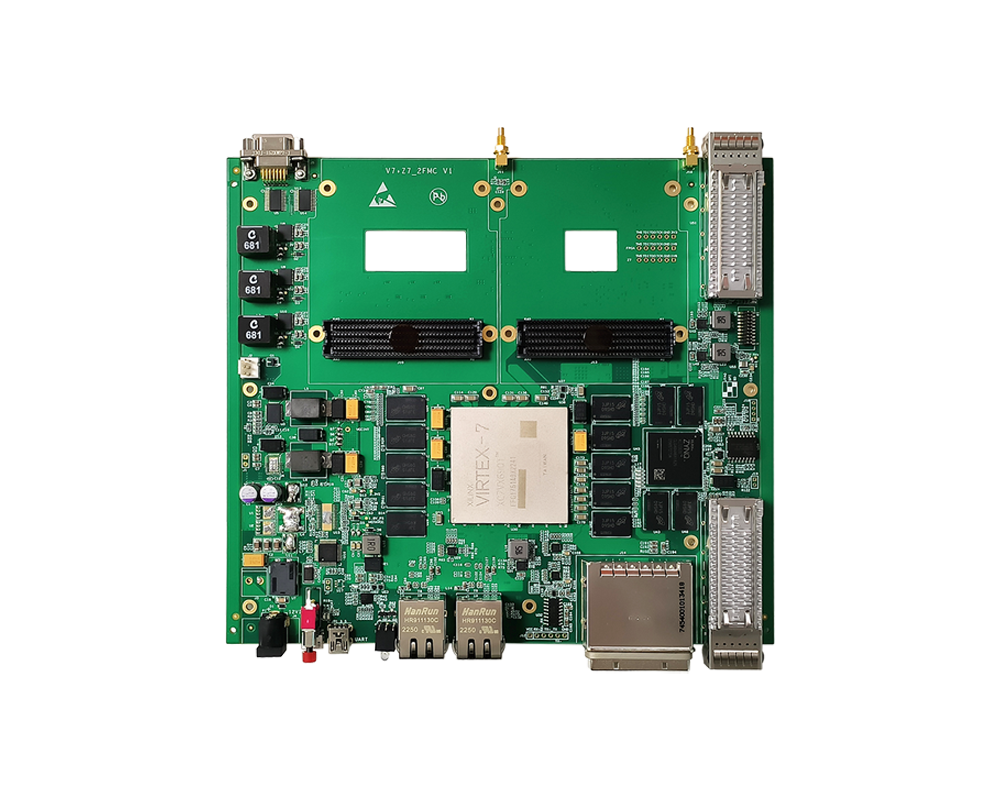

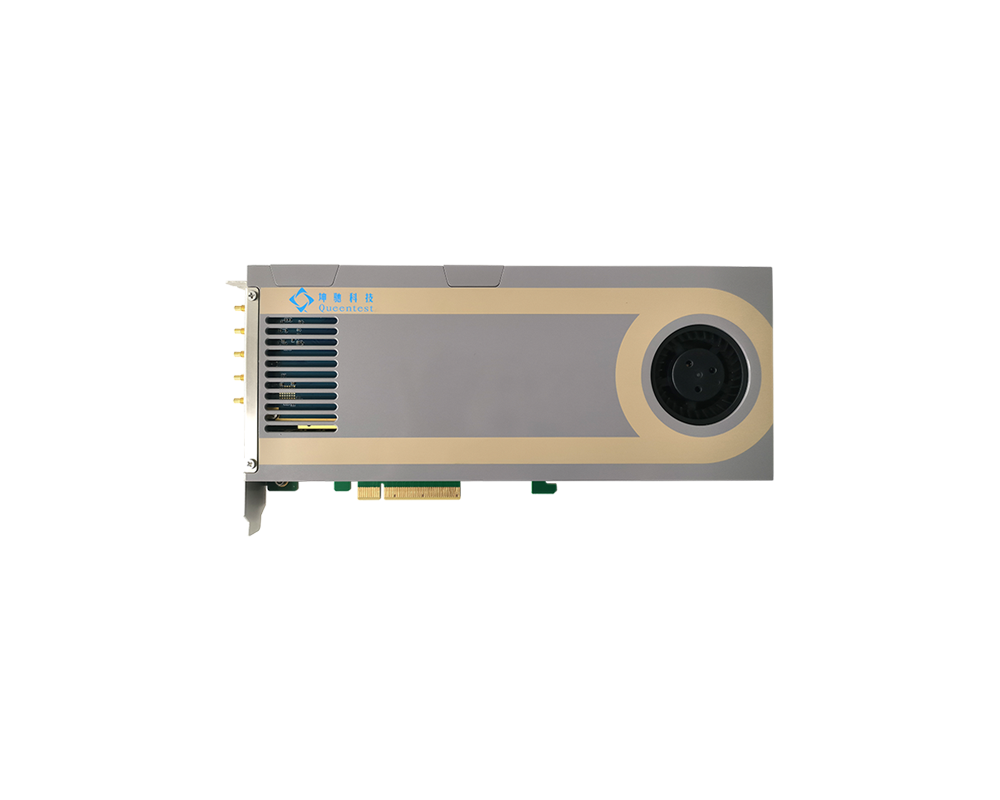

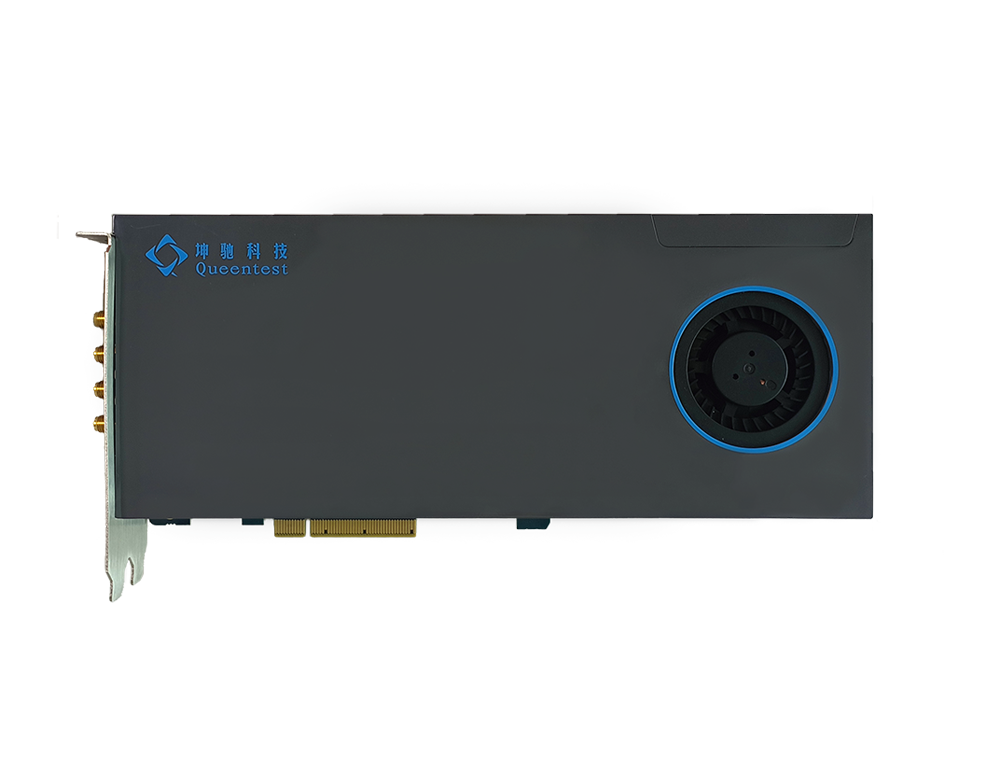

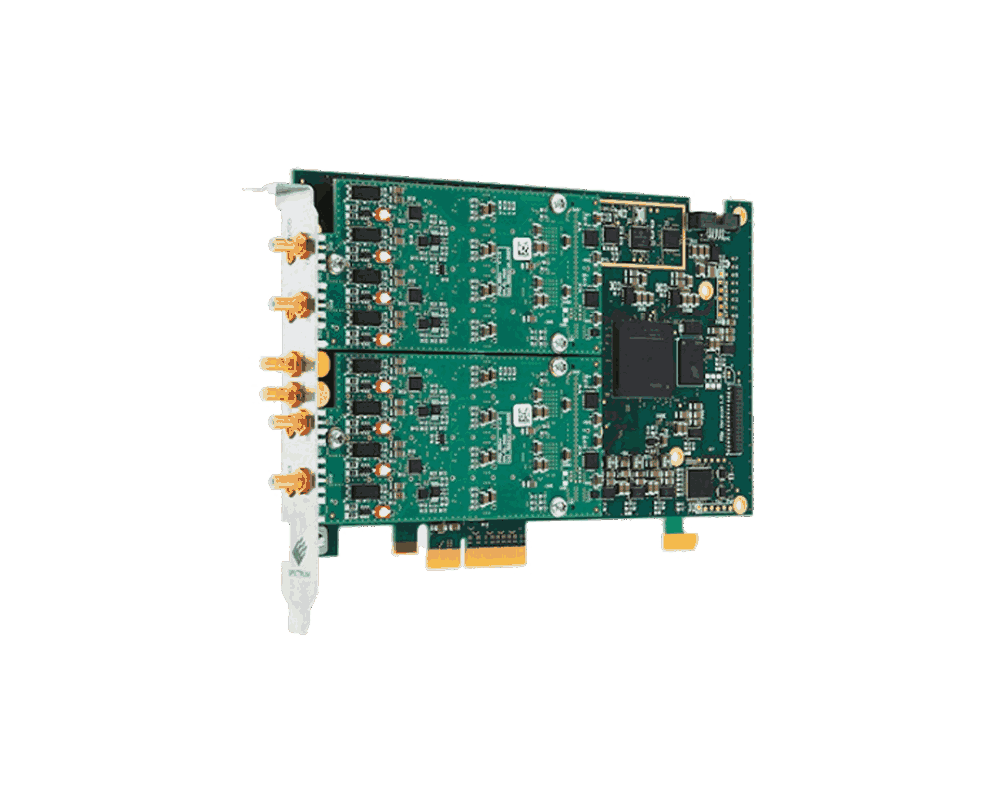

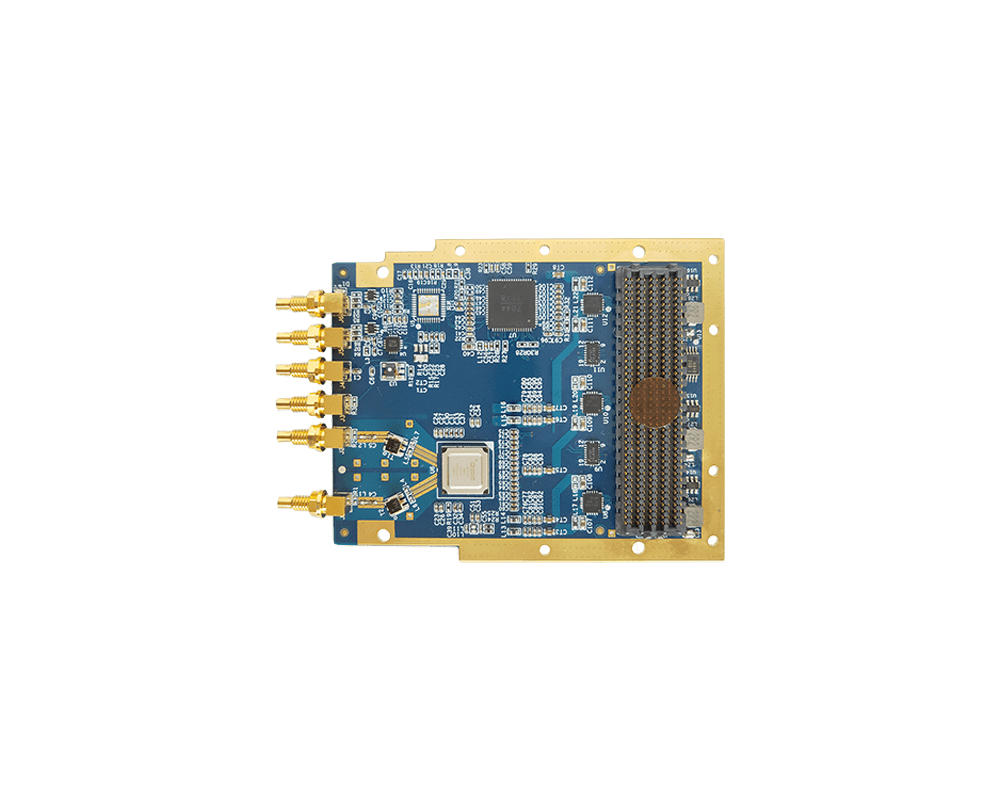

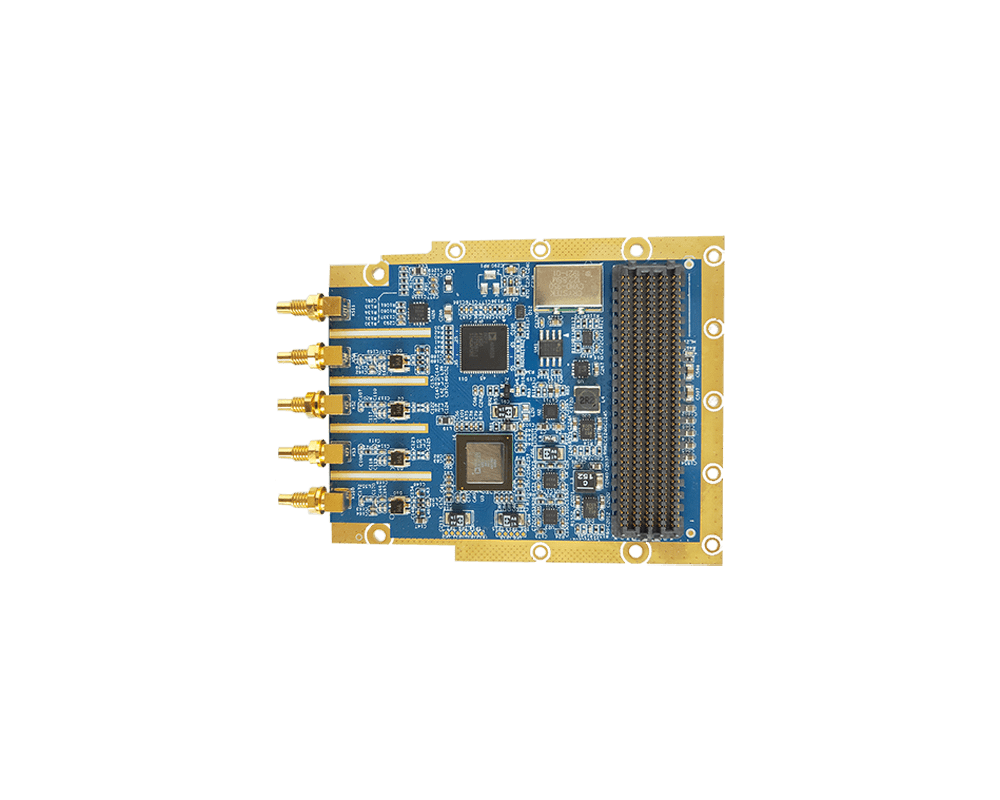

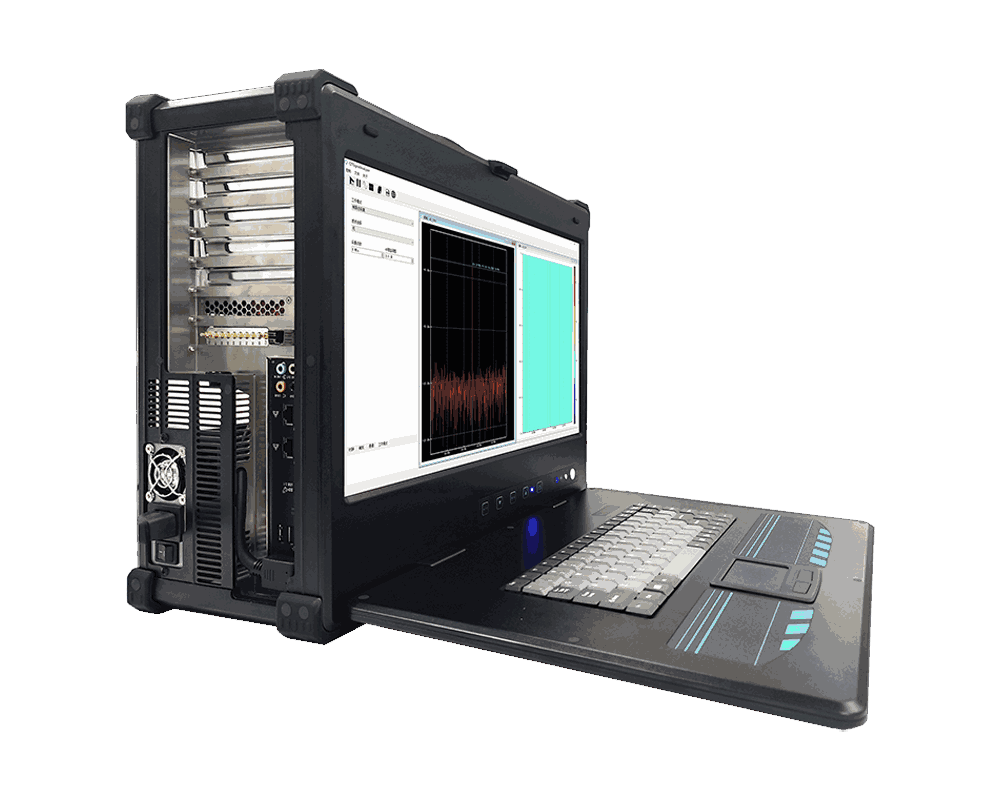

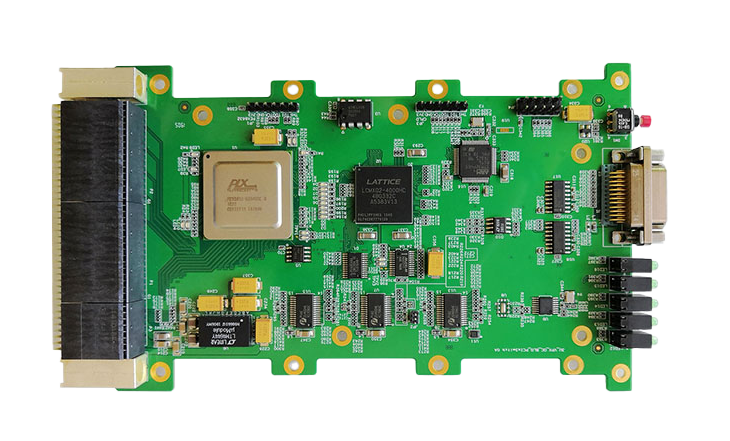

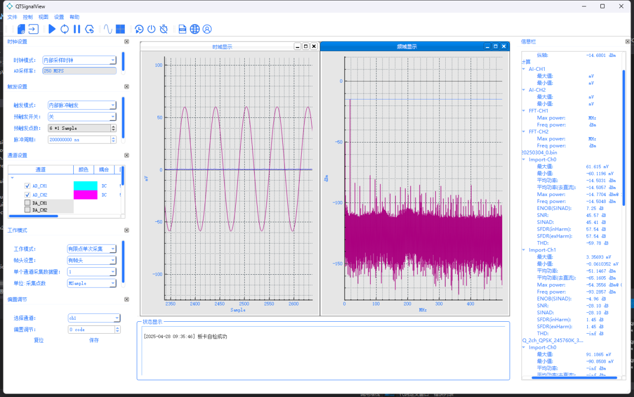

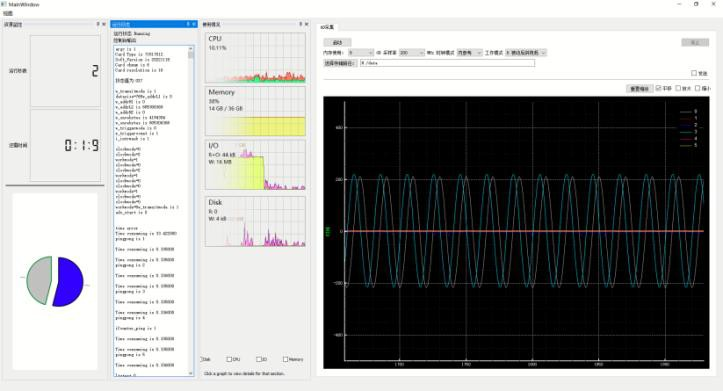

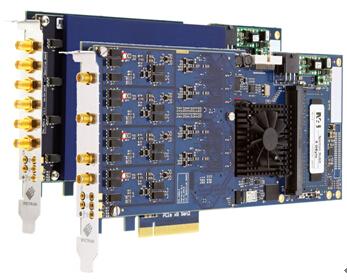

當(dāng)然,數(shù)據(jù)傳輸速度并不簡(jiǎn)單地依賴于數(shù)字化儀總線,。它還會(huì)受到其它因素的影響,,譬如PC、PC的設(shè)置以及用于控制傳輸處理的軟件,。圖1顯示了德國Spectrum公司的M4i.22xx和M4i.44xx系列數(shù)字化儀,,它們?cè)?位分辨率下的采樣率高達(dá)5 GS/s、14位分辨率下達(dá)到500 MS/s或16位分辨率下達(dá)到250 MS/s,。這些M4i系列卡片均具備搭配數(shù)字化儀的新PC總線技術(shù),,PCIe x8通路二代接口能以高達(dá)3.4 GB/s的速度從板上存儲(chǔ)器向PC傳輸數(shù)據(jù)。M4i系列板卡配有為Windows和LINUX提供的速度優(yōu)化驅(qū)動(dòng)以及總線主控裝置,,用以保持快的吞吐率,。

圖1. 德國Spectrum公司的M4i.22xx和M4i.44xx系列數(shù)字化儀速度快且分辨率高,使用高速PCle x8通路二代接口能使傳輸速度達(dá)到3.4 GB/s

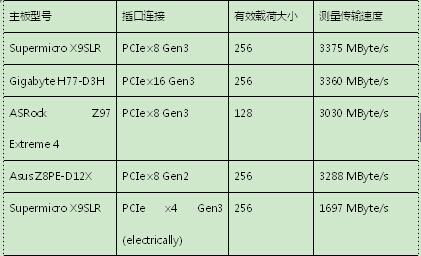

表格2顯示了M4i系列數(shù)字化儀在不同PC主板和配置下運(yùn)行的基準(zhǔn)測(cè)試結(jié)果,。當(dāng)PCle有效載荷大小為256 Byte時(shí)效果達(dá)到優(yōu),。主板說明解釋了如何進(jìn)行插口電氣連接,因?yàn)椴皇敲總€(gè)機(jī)械8通路插口都與所有通路連接在芯片組上,。

除了快速的PCle總線,,M4i數(shù)字化儀卡片也配有不同的采集模式。標(biāo)準(zhǔn)采集模式使用板上采集存儲(chǔ)作為環(huán)形緩沖區(qū),,就像示波器一樣,。數(shù)據(jù)被寫入數(shù)字化儀的環(huán)形存儲(chǔ)器直至觸發(fā)事件發(fā)生。觸發(fā)產(chǎn)生后,,后觸發(fā)值被記錄下來,。前觸發(fā)值和后觸發(fā)值均會(huì)被囊括在記錄數(shù)據(jù)中。

智能讀取模式

另一種采集模式是FIFO(先進(jìn)先出式),。這是為數(shù)字化儀和外部主機(jī)之間進(jìn)行連續(xù)數(shù)據(jù)傳輸而設(shè)計(jì)的一種流模式,。對(duì)數(shù)據(jù)流的控制由驅(qū)動(dòng)器基于中斷請(qǐng)求自動(dòng)完成。

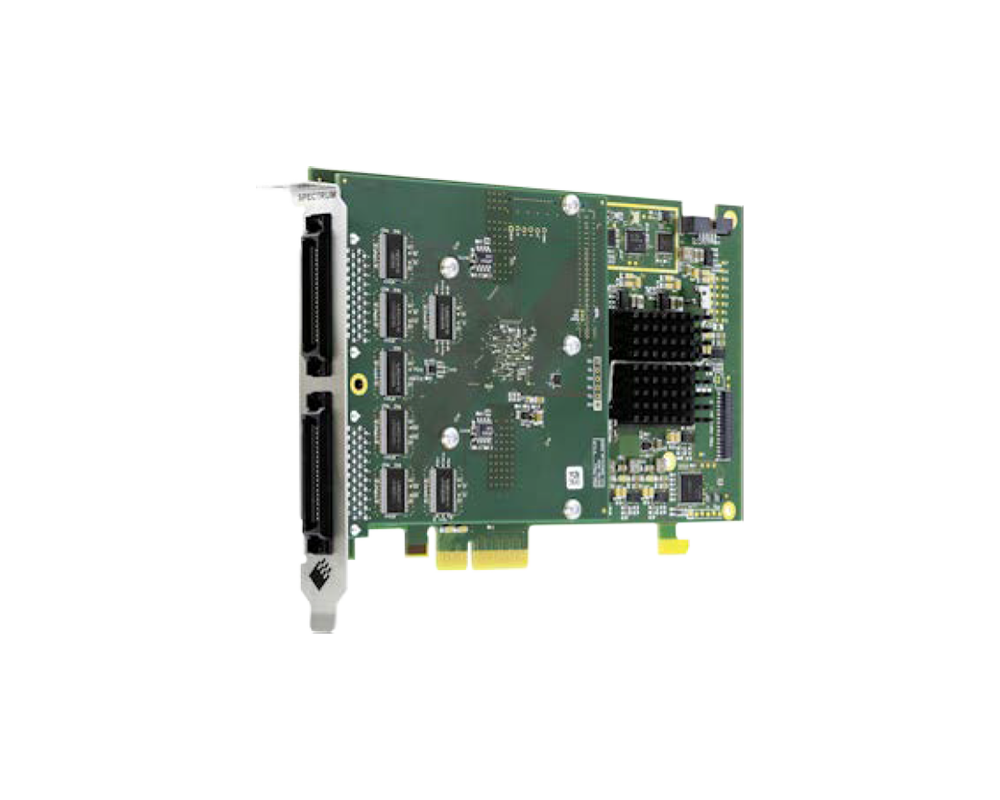

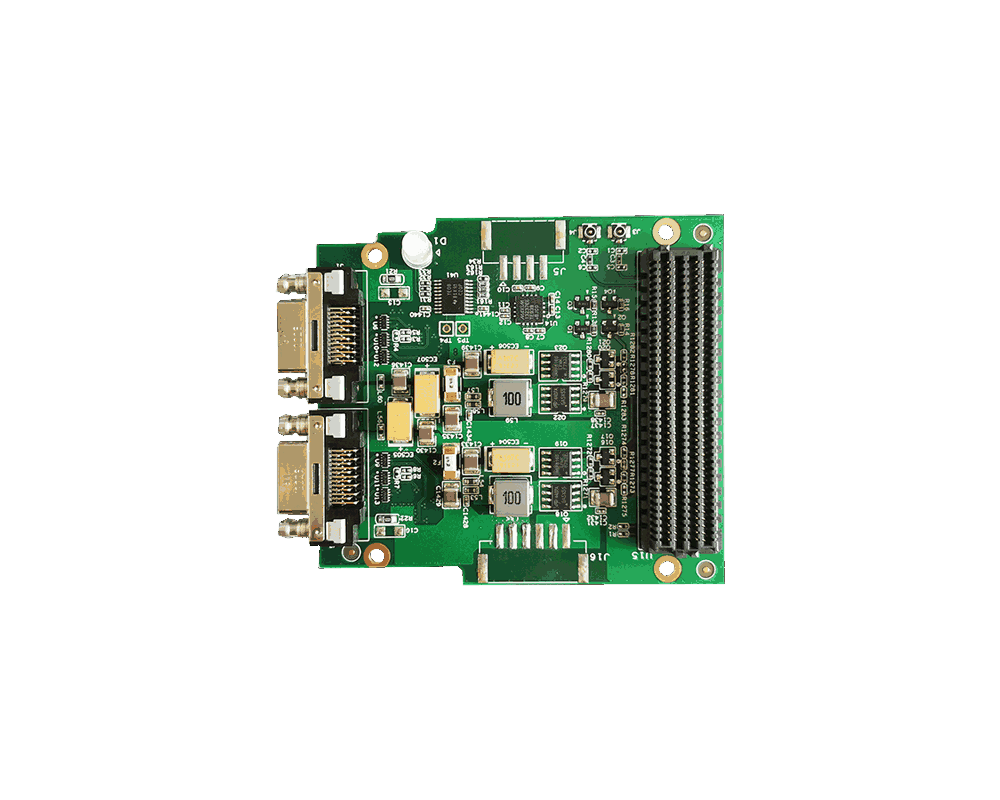

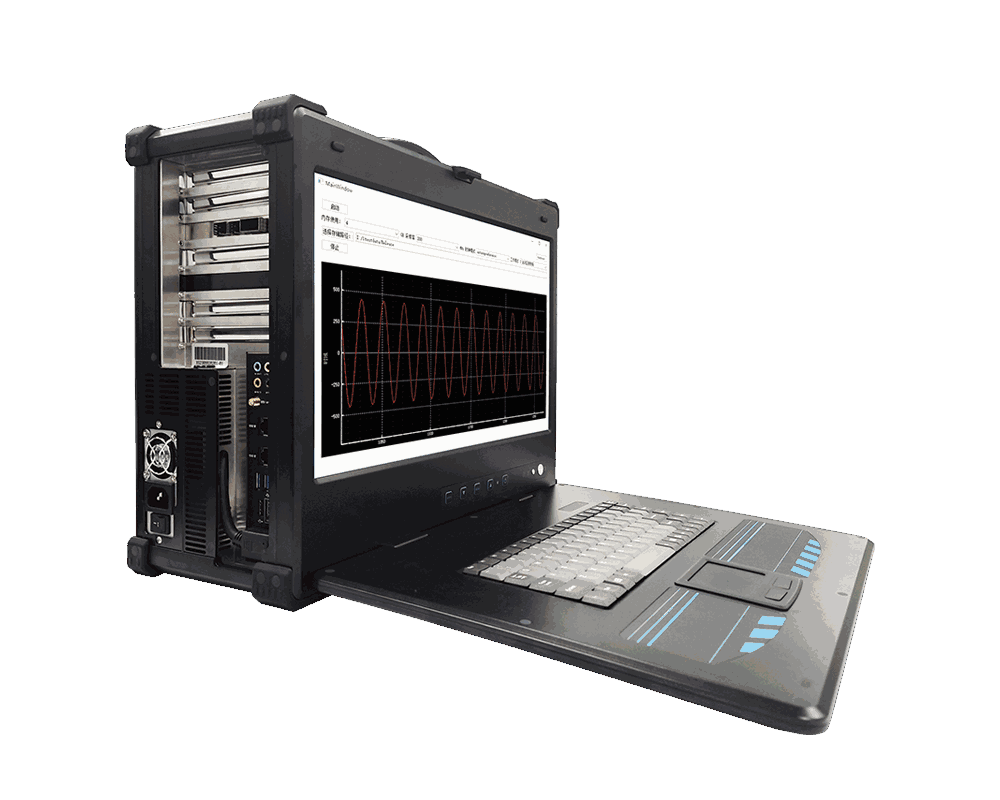

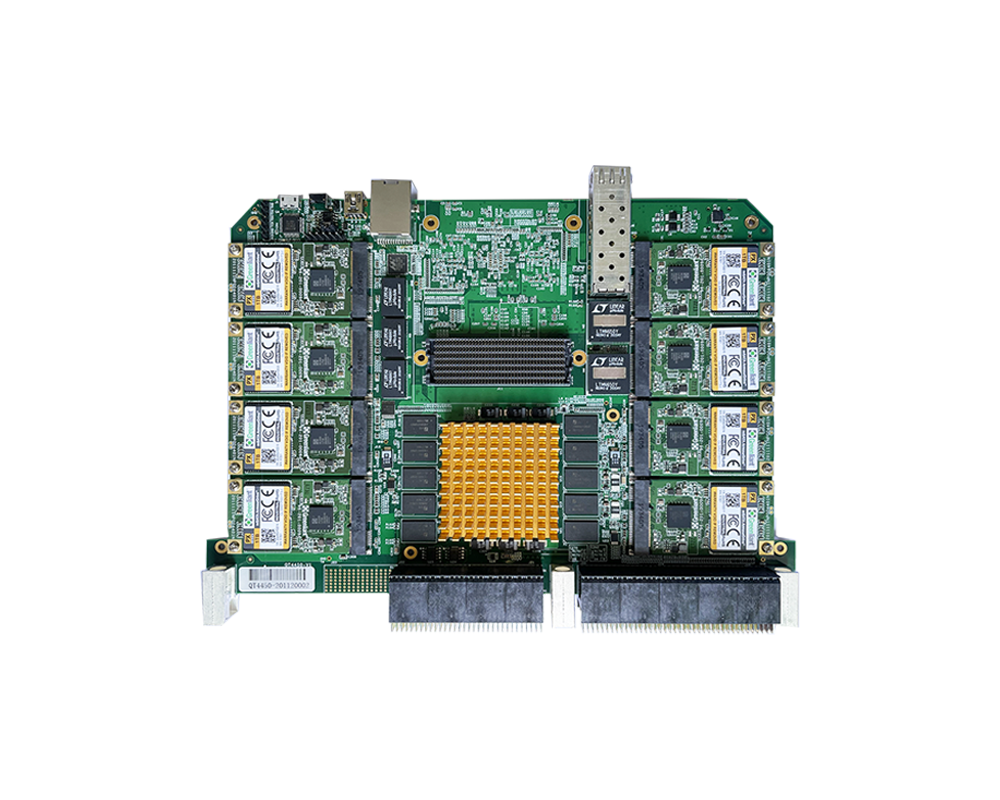

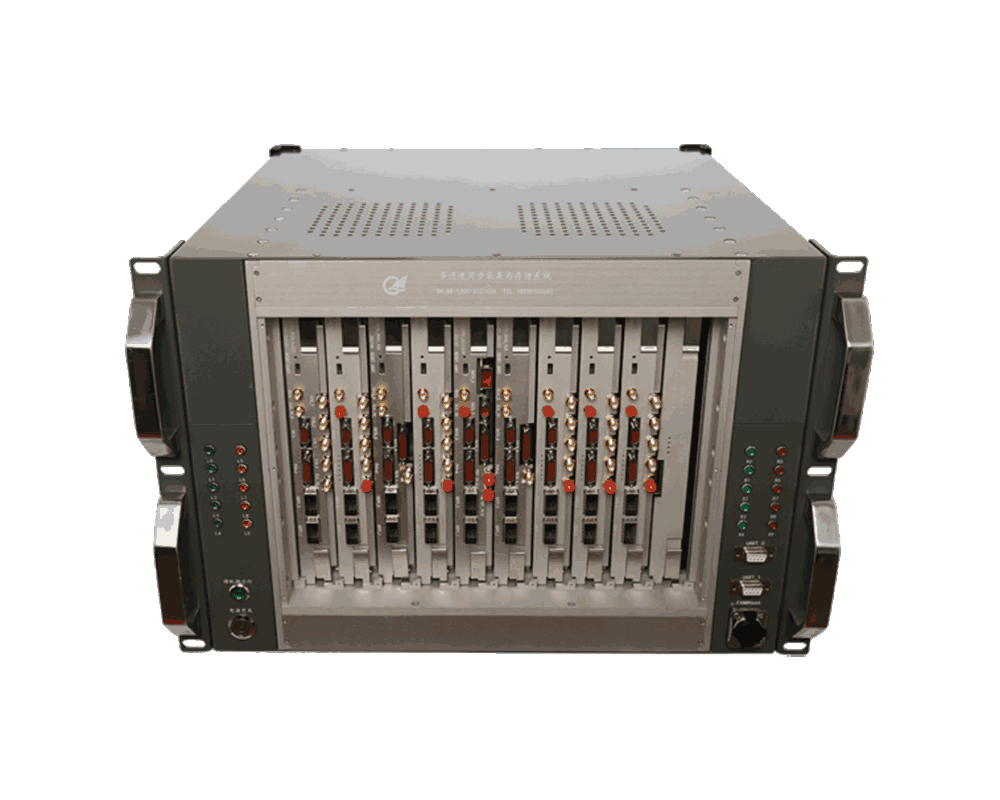

標(biāo)準(zhǔn)模式與FIFO模式的主要區(qū)別在于,,標(biāo)準(zhǔn)模式受限于M4i系列產(chǎn)品4GB板上存儲(chǔ)器的使用率,。FIFO模式旨在從總線向PC存儲(chǔ)器或硬盤連續(xù)傳輸數(shù)據(jù),進(jìn)而運(yùn)行更長的采集時(shí)間,。完全內(nèi)置的采集存儲(chǔ)器使用起來就像一個(gè)緩沖區(qū),,可以提供可靠的數(shù)據(jù)流。要想使流達(dá)到佳狀態(tài)需要一個(gè)專用的RAID控制器,,一束帶有高吞吐量的SSD,,一個(gè)優(yōu)化驅(qū)動(dòng)器,適當(dāng)?shù)南到y(tǒng),,軟件以及可以避免操作系統(tǒng)瓶頸的流軟件,。德國Spectrum公司能夠提供一套完整的解決方案,如圖2所示,,容許幾個(gè)TB的數(shù)據(jù)流連續(xù)向SSD陣列以大于 3 GB/s的速度傳輸,。

容許幾個(gè)TB的數(shù)據(jù)流連續(xù)向SSD陣列以大于 3 GB/s的速度傳輸。

圖2. Spectrum的流系統(tǒng)SPcB8-E6可以包括多達(dá)6個(gè)Spectrum卡片,,存儲(chǔ)量高達(dá)3GB/s至8TB且擁有多個(gè)流選項(xiàng)

低占空比測(cè)量的存儲(chǔ)分段模式

標(biāo)準(zhǔn)模式和FIFO模式還能用于三種不同的多重記錄法,。無論模擬信號(hào)轉(zhuǎn)化為數(shù)字信號(hào)的過程是集中式的還是連續(xù)的,都適用于多重記錄法,。多重記錄可以更有效的使用板上采集存儲(chǔ)器,,特別是對(duì)低占空比測(cè)量的應(yīng)用。低占空比應(yīng)用包括那些短時(shí)事件,,隨后伴隨長時(shí)間靜態(tài)間隔,。捕捉此類信號(hào)的佳采集方法就是多重記錄(分段)模式、門控模式和ABA(雙時(shí)基)采集,。這些模式都采用分割存儲(chǔ)器的方式進(jìn)行多重采集,。這種雙時(shí)基ABA模式降低了觸發(fā)器之間的采樣率,,節(jié)省了存儲(chǔ)空間,但也為觸發(fā)器之間的空載時(shí)間提供了一個(gè)可視化的選項(xiàng),。

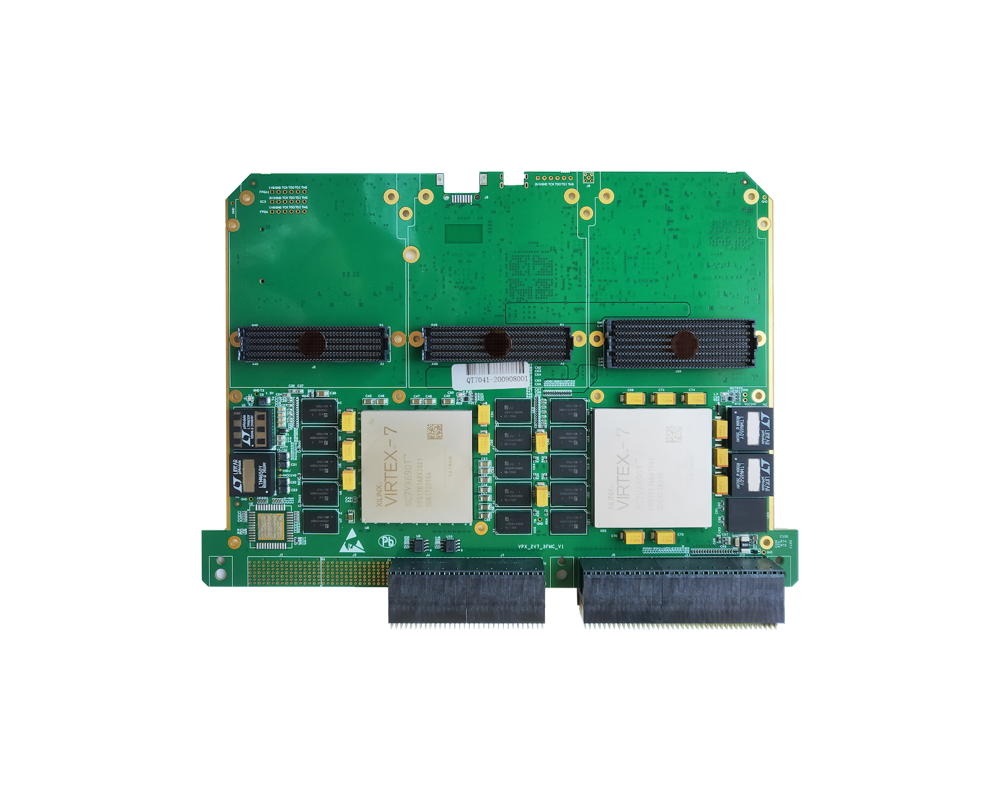

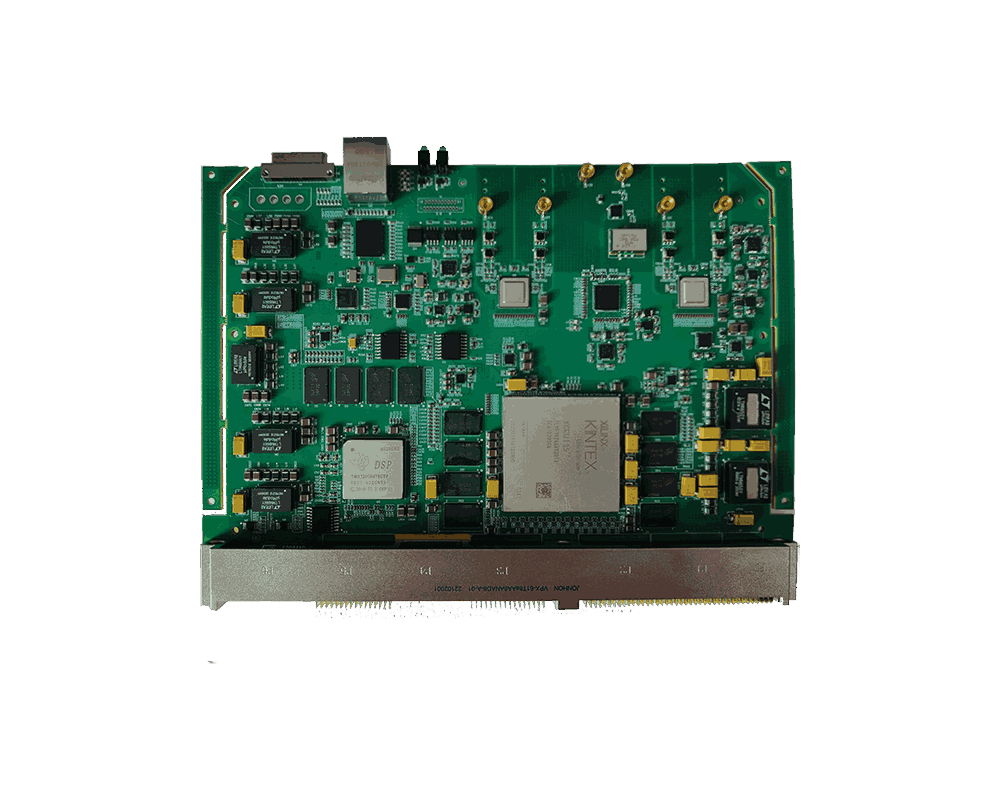

板上分析

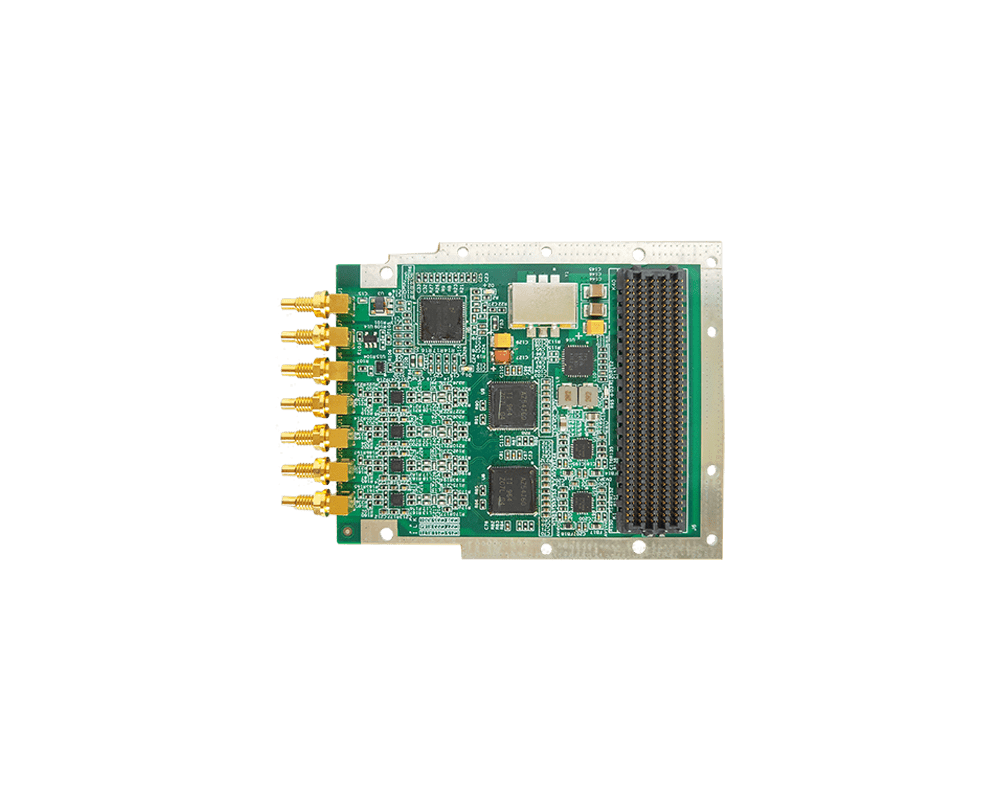

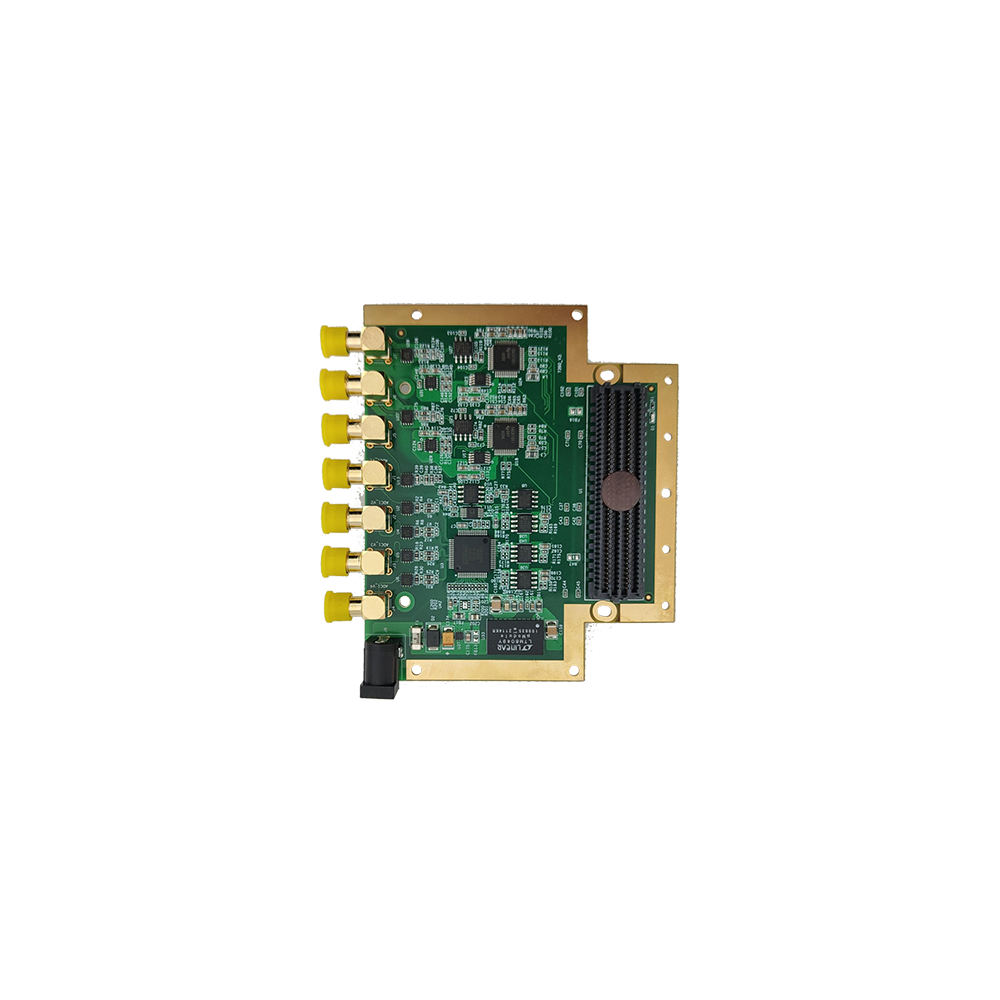

使用M4i系列數(shù)字化儀解決數(shù)據(jù)瓶頸的后一個(gè)方法是使用板上處理和數(shù)據(jù)簡(jiǎn)化,。M4i系列卡片的設(shè)計(jì)中含有FPGA,可以使用包括存儲(chǔ)控制,、觸發(fā)模式,、PCle總線控制和信號(hào)處理等一系列功能。圖3顯示了M4i系列數(shù)字化儀的方框圖和基本結(jié)構(gòu),。FPGA空間內(nèi)部被預(yù)留出來,,因此諸如信號(hào)平均、峰值檢波以及統(tǒng)計(jì)功能等廠商開發(fā)固件可以在此運(yùn)行,。

板上信號(hào)處理可以減少按量級(jí)需要向PC傳輸?shù)慕K的數(shù)據(jù)總量,。比如,在使用循環(huán)信號(hào)時(shí),,平均固件能夠累積超過65,000個(gè)獨(dú)立波形,,每個(gè)波形可達(dá)128k點(diǎn)長。這種功能有效地減少了從所有獨(dú)立波形向單個(gè)平均波形傳輸?shù)臄?shù)據(jù),。

圖3. M4i數(shù)字化儀系列產(chǎn)品顯示了FPGA的信號(hào)處理路徑

同樣,,峰值檢測(cè)固件可以定位信號(hào)中的大和小事件,將它們的值和對(duì)應(yīng)的時(shí)間信息存儲(chǔ)在一起,。通過這種方法,,先前含有數(shù)千甚至數(shù)百萬數(shù)據(jù)點(diǎn)的波形可以減少到一組簡(jiǎn)單的,也許只有6到8個(gè)的基本數(shù)據(jù)集,。

小結(jié)

隨著ADC技術(shù)在現(xiàn)代數(shù)字化儀中的應(yīng)用,,實(shí)現(xiàn)了更快的采集速度、更高的分辨率,,需要被采集,、存儲(chǔ)和傳輸?shù)絇C的數(shù)據(jù)量不斷增加。將數(shù)據(jù)轉(zhuǎn)移至PC進(jìn)行查看,、存儲(chǔ)和分析需要具有合適總線(持續(xù)可比的數(shù)據(jù)傳輸速度)的數(shù)字轉(zhuǎn)換設(shè)備,、靈活的采集和傳輸模式、配置良好的PC和恰當(dāng)?shù)能浖?。在極端情況下,,有必要減少數(shù)據(jù)時(shí),可以使用FPGA技術(shù),。