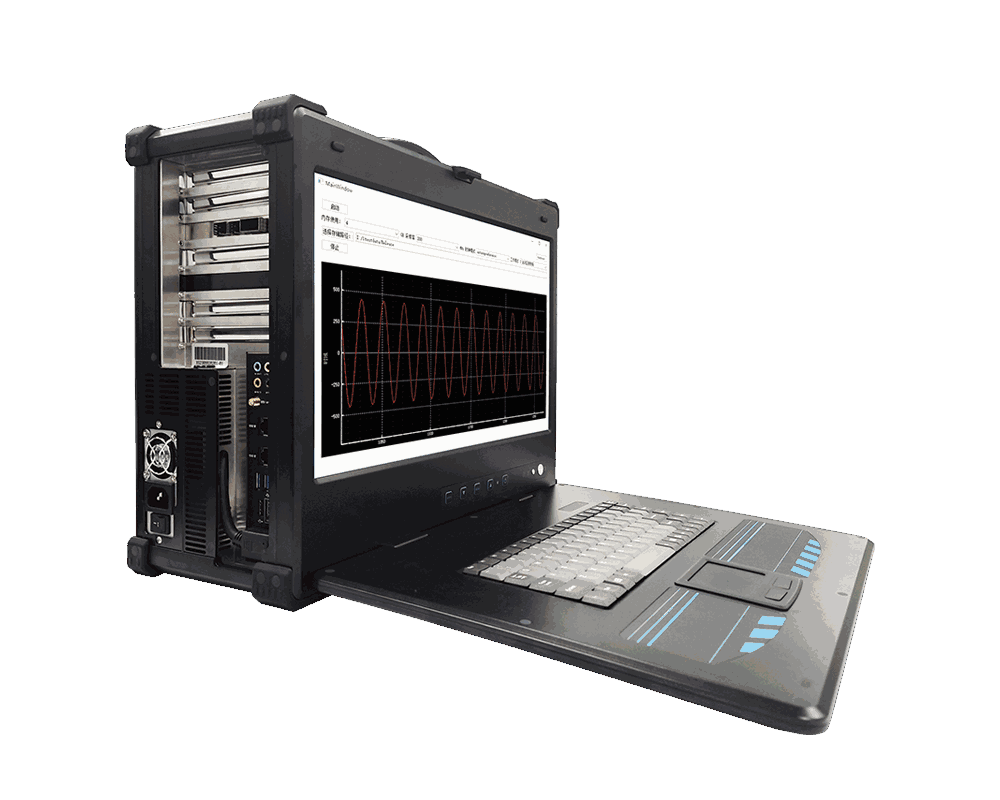

局放數(shù)據(jù)采集測試系統(tǒng)

1.概述

該系統(tǒng)主要應(yīng)用于局放傳感器的信號采集及分析,,實現(xiàn)在線和離線局放監(jiān)測。

1.1采集系統(tǒng)規(guī)格:

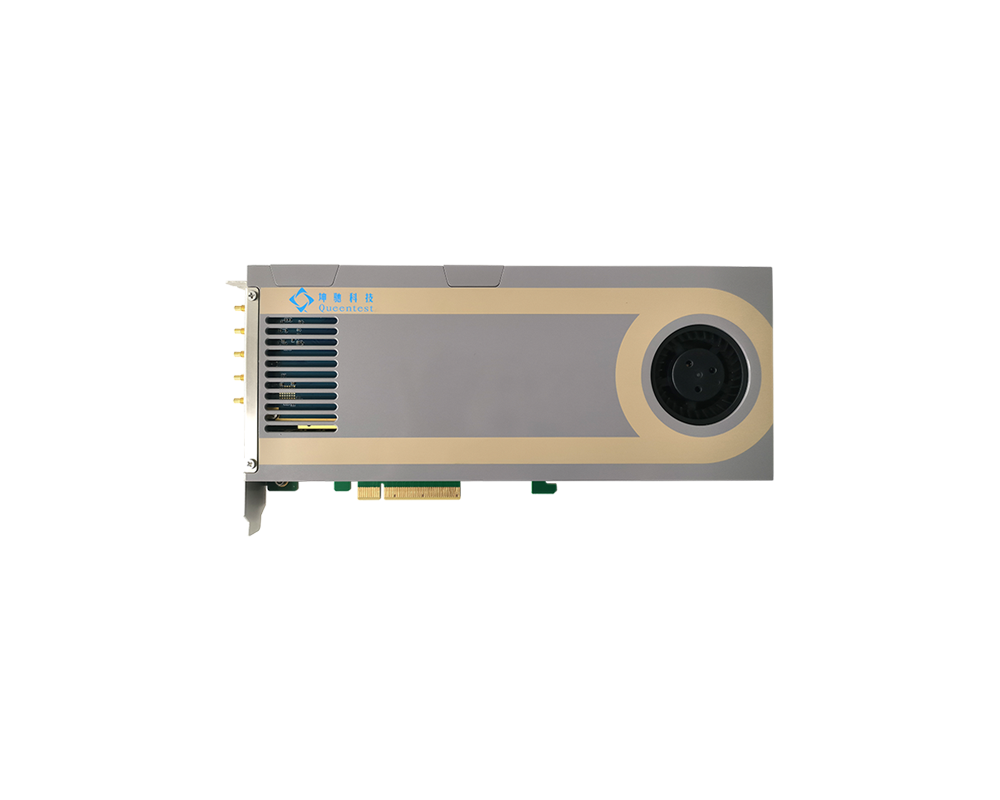

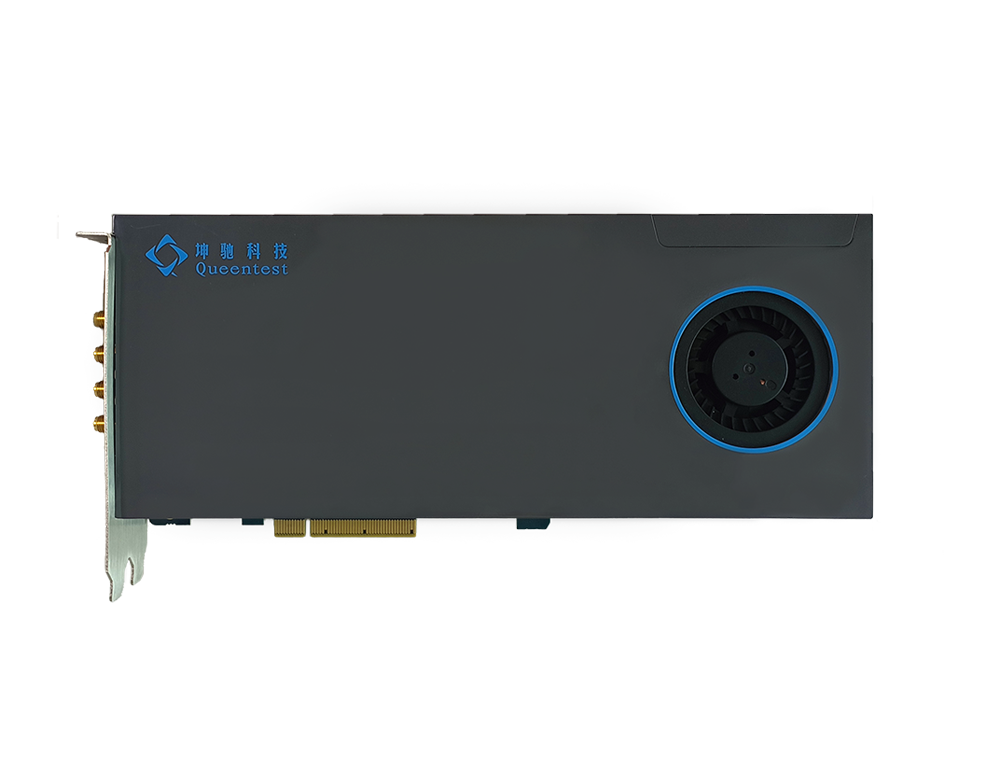

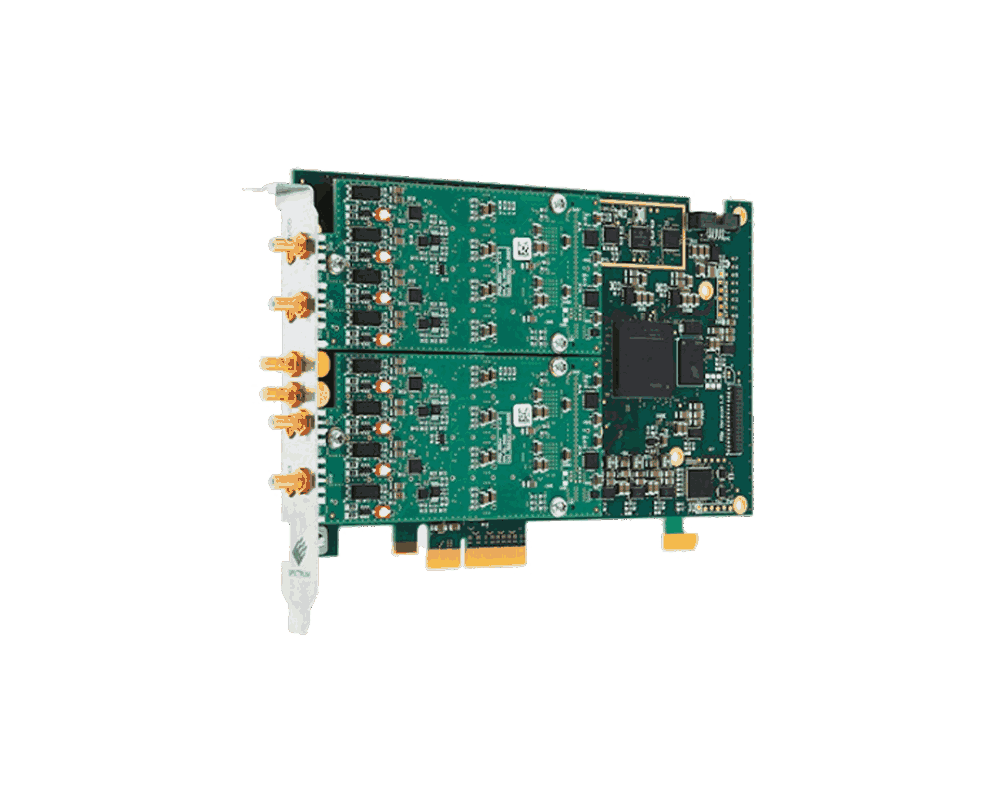

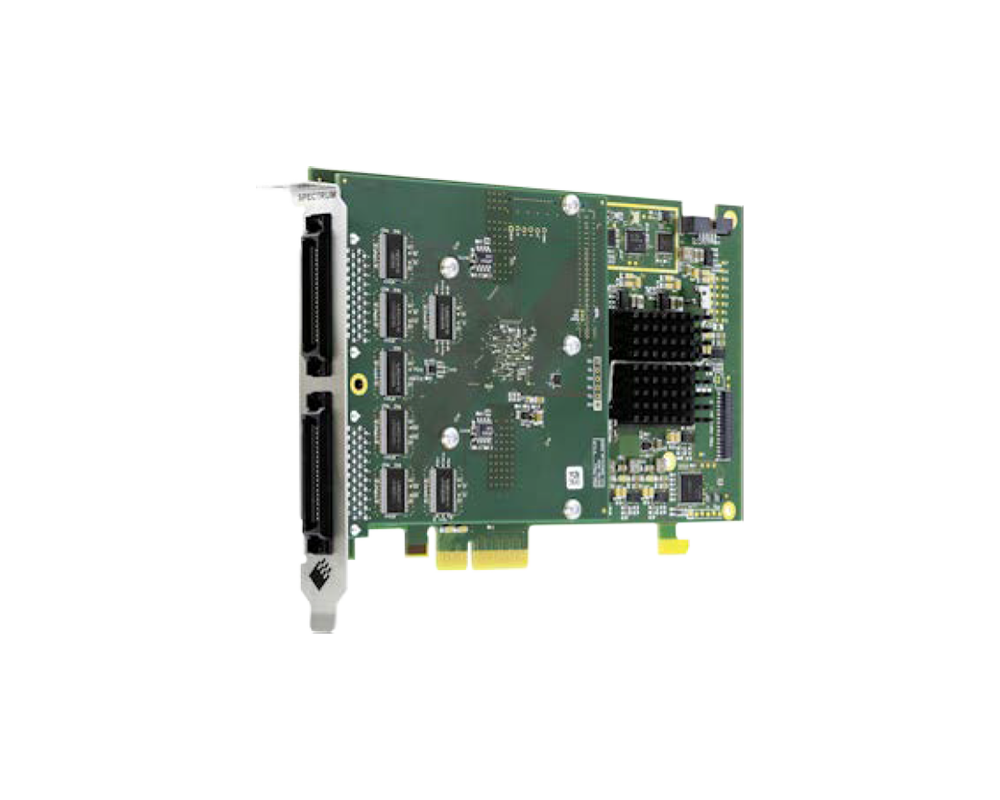

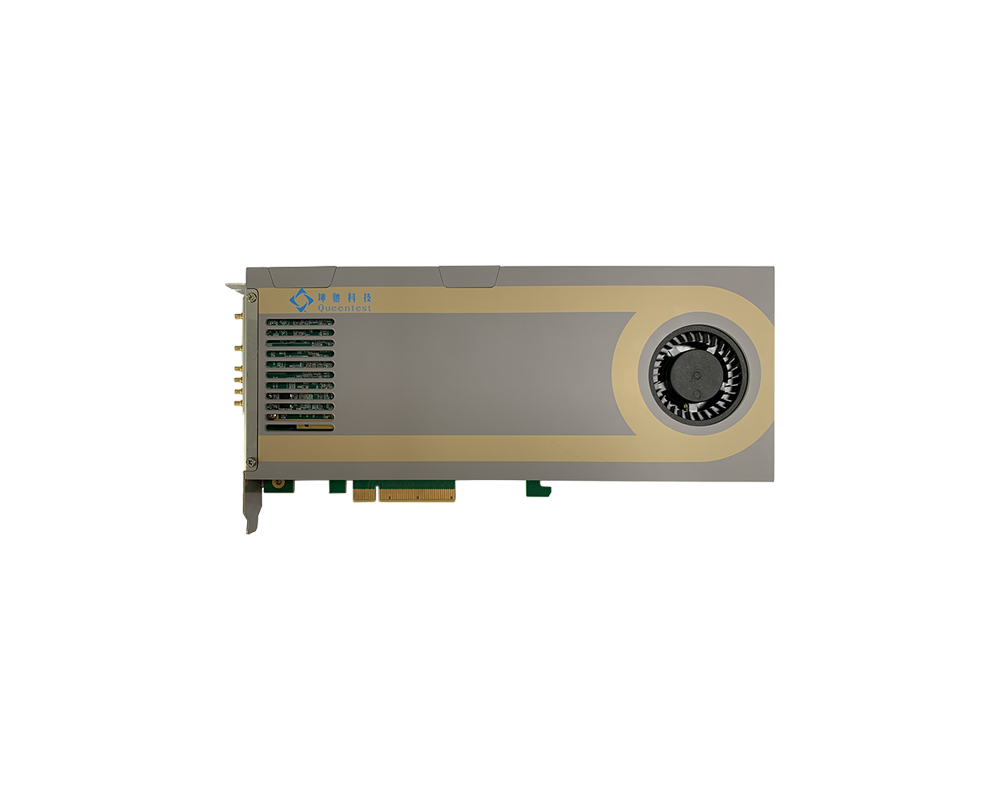

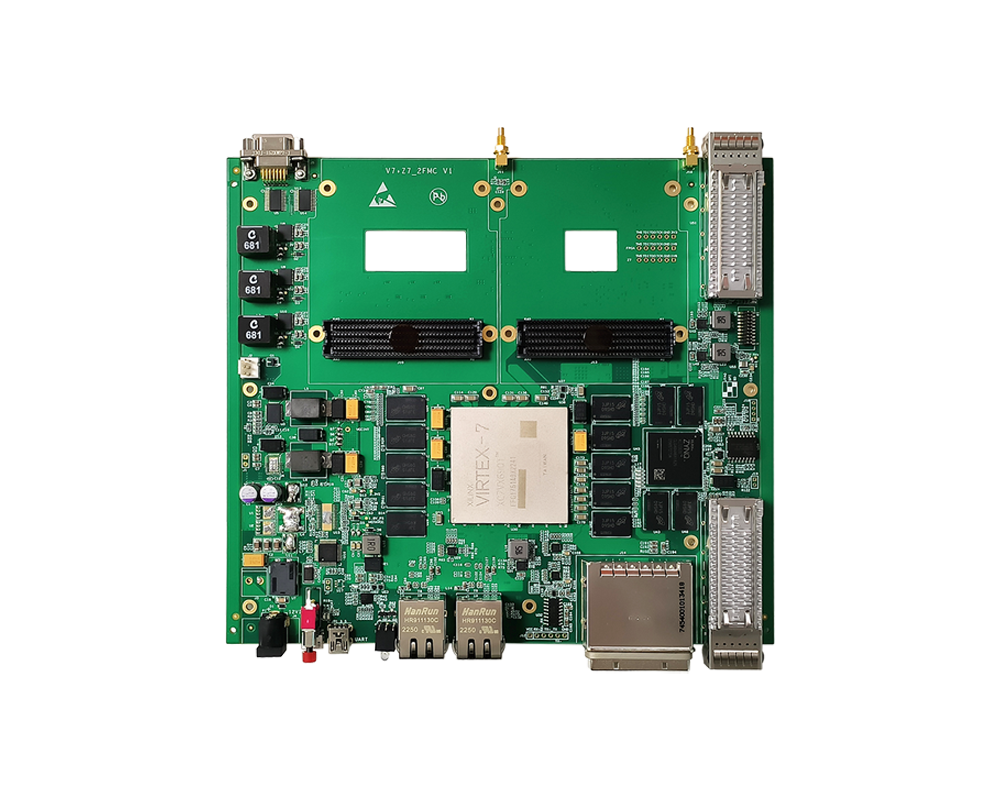

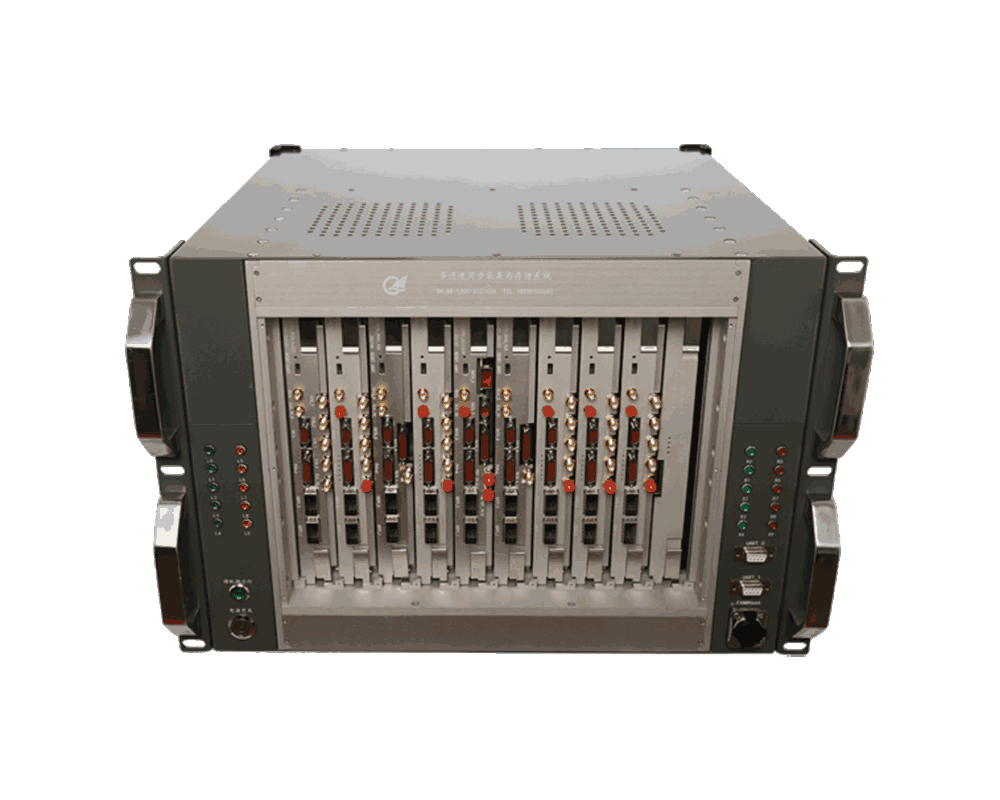

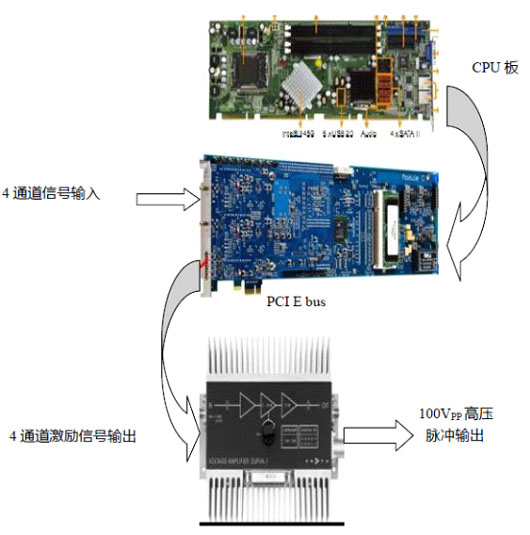

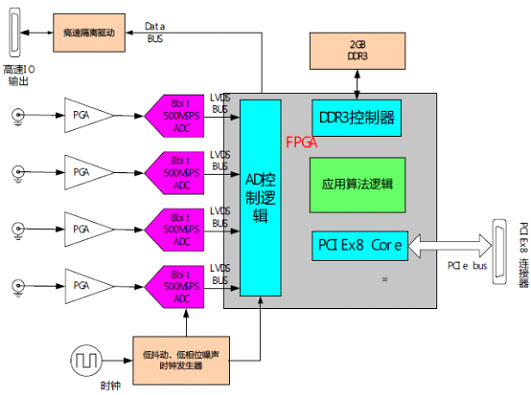

系統(tǒng)基于PCIExpress總線結(jié)構(gòu),,包括如下幾個部分:

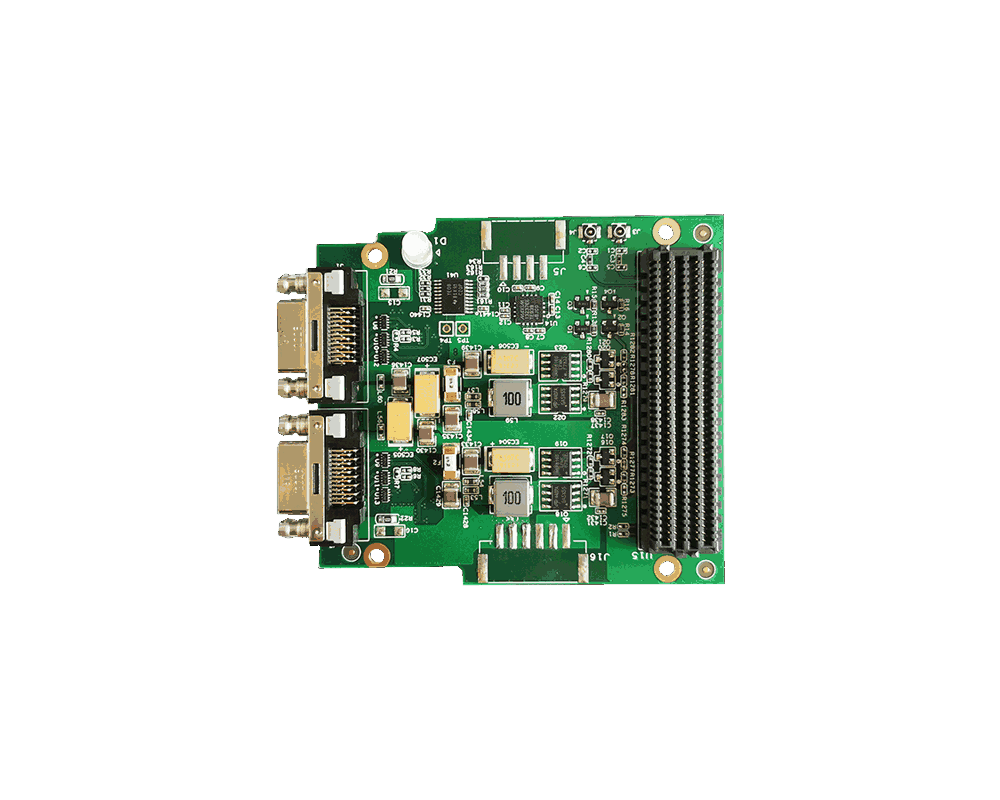

1.1.14通道8bit500Msps同步采集,,標(biāo)準(zhǔn)PCIe全長卡尺寸;

1.1.24個高速IO,,產(chǎn)生激勵脈沖輸出,。

1.1.3外置脈沖放大器,輸出100Vpp的激勵短脈沖,。

1.1.4基于PCIExpressx8總線的工控機,。

1.2采集系統(tǒng)實現(xiàn)框圖:

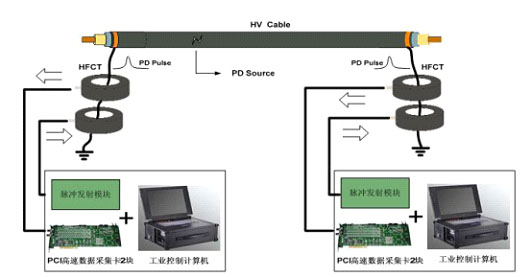

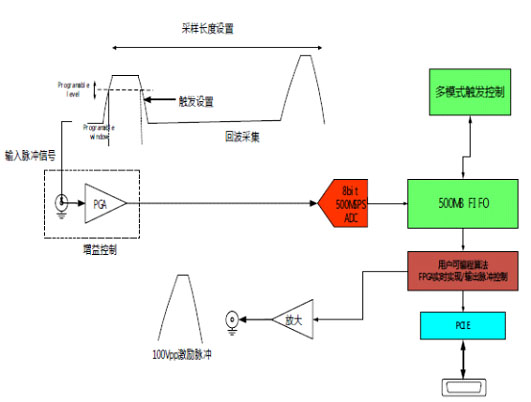

1.3采集系統(tǒng)原理框圖:

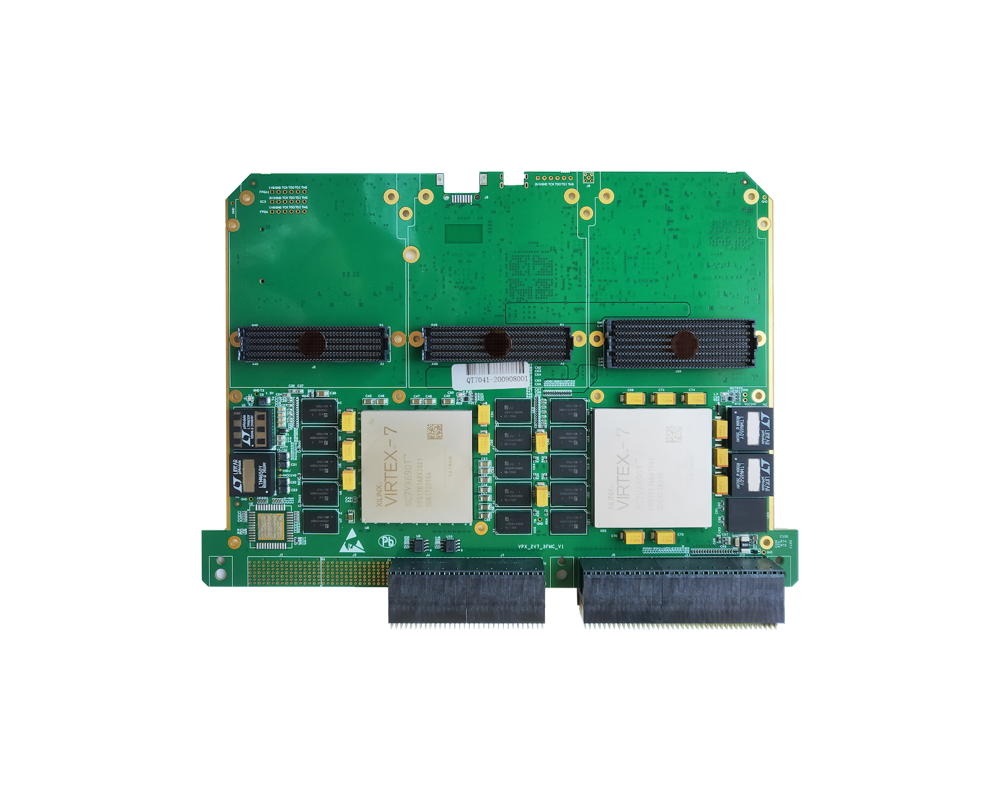

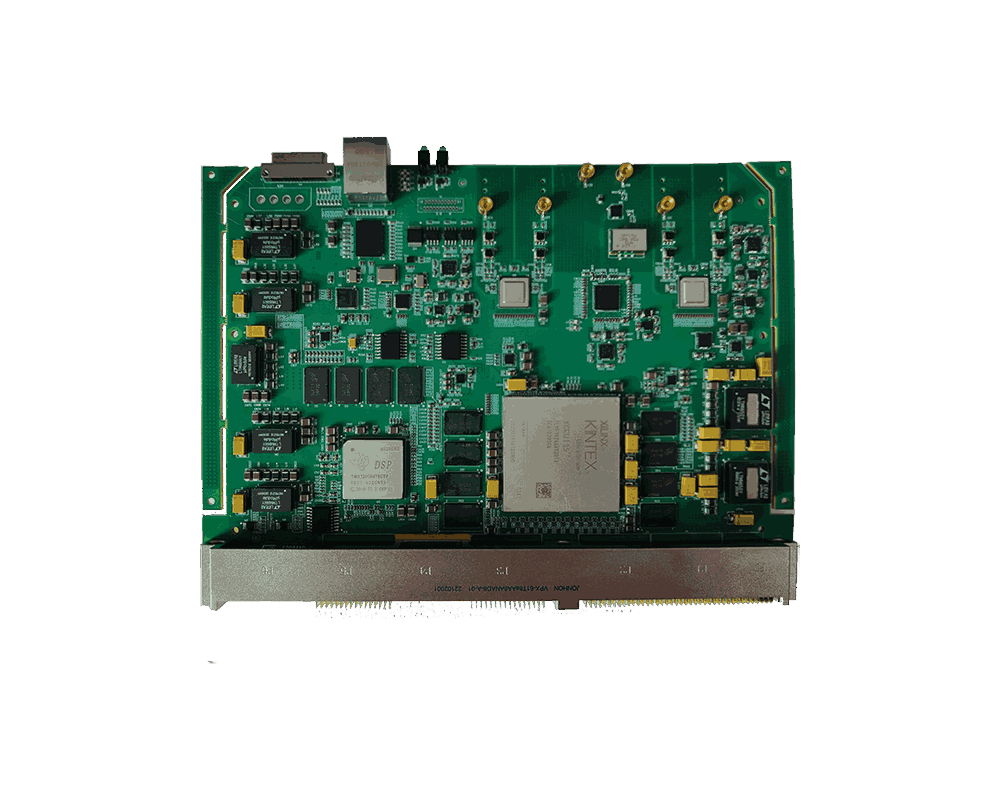

1.4數(shù)據(jù)采集卡特性:

1.4.14通道8bit500MSPS同步采集。

1.4.24通道程控增益放大器,,增益倍數(shù)0-100倍調(diào)整,,滿幅度輸出1Vpp。

1.4.3輸入通道DC耦合,,50歐姆輸入阻抗,。

1.4.4模擬輸入帶寬DC-120MHz/-3dB,。

1.4.5輸入端口過壓保護,允許200W/20us浪涌功率輸入,。

1.4.62GB本地緩存,,保證每次觸發(fā),每通道有0.5S的采集時間,。

1.4.7支持PCIEx8接口,,連續(xù)數(shù)據(jù)傳輸率1000MB/s。

1.4.8低抖動,、低相噪時鐘發(fā)生器,。

1.4.9可以多塊卡組成多通道同步工做模式。

1.5系統(tǒng)工作模式:

1.5.1觸發(fā)設(shè)置:可以根據(jù)輸入脈沖的幅度和寬度設(shè)置觸發(fā)判決條件,。

1.5.2輸入放大倍數(shù)可以通過軟件設(shè)置,。

1.5.3輸出脈沖相對于觸發(fā)事件時間可以設(shè)置,小單位為2ns,。

1.5.4出脈沖和觸發(fā)事件條件隨機延遲不超過4個采樣點,,及8ns。

1.5.5觸發(fā)后,,采集長度可以設(shè)置,,大每通道可以采集500M個點。

1.5.6可以回傳長度為500M個點的原始波形供計算機軟件分析,。

1.6脈沖發(fā)生:

1.6.1性能指標(biāo):

1.6.1.1電源:AC90V-260V

1.6.1.2輸出功率:瞬時20KW

1.6.1.3平均功率:小于300W

1.6.1.4輸出脈沖幅值:100V,500V,,1000V三檔可選,在50?時

1.6.1.5輸出脈沖寬度:100ns-10us

1.6.1.6觸發(fā)單元脈沖延遲:375ns+/-5%

1.6.1.7脈沖發(fā)生器脈沖延遲:750ns+/-5%

1.6.1.8可設(shè)置輸出脈沖延遲:25ms

1.6.1.9觸發(fā)門檻范圍(上限):5mV~150mV

1.6.1.10觸發(fā)門檻范圍(上限):100mV~1000mV

1.6.1.11觸發(fā)極性:正脈沖或負(fù)脈沖

1.6.1.12輸入帶寬:50MHz

1.6.1.13輸入抑制:當(dāng)沒有輸入時,,將每100秒發(fā)出脈沖消除反射脈沖重新觸發(fā)裝置

1.6.1.14自由運行模式:在固定間隔內(nèi)連續(xù)產(chǎn)生脈沖

1.6.1.15自由運行模式時間間隔:1毫秒,,1秒,1分鐘

1.6.1.16輸入/輸出保護:采用氣體放電管保護

1.6.1.17輸入輸出連接:BNC接口

1.6.1.18電源:電池供電,,10小時連續(xù)供電

1.6.2通信方式:

1.6.2.1采用串行通信方式:

通過一個控制口和一根地線串行控制脈沖電源

1.6.2.2可接受電平:3.3V5V或10V(認(rèn)可信號:低電平小于1V高電平大于2V)

1.6.2.3約定控制信號三個8位數(shù)據(jù)段,,每個位(bit)1US,高電平為1低電平為0,。

停止位為1位起始位為1位,。

個8位段發(fā)送:255(11111111)

用來表示啟始同步。每收到這個信號,,接收器將接收并認(rèn)可接下來的三個命令段,。

第二個8位段:

表示脈沖寬度?;鶖?shù)0.1us(100ns)比如發(fā)20(00010100)代表脈沖寬度為2us,。

大認(rèn)可100(01100100)即10us。

第三個8位段:

表示電壓檔位選擇。1(00000001)代表100V2(00000010)代表500V3(00000011)代表1000V

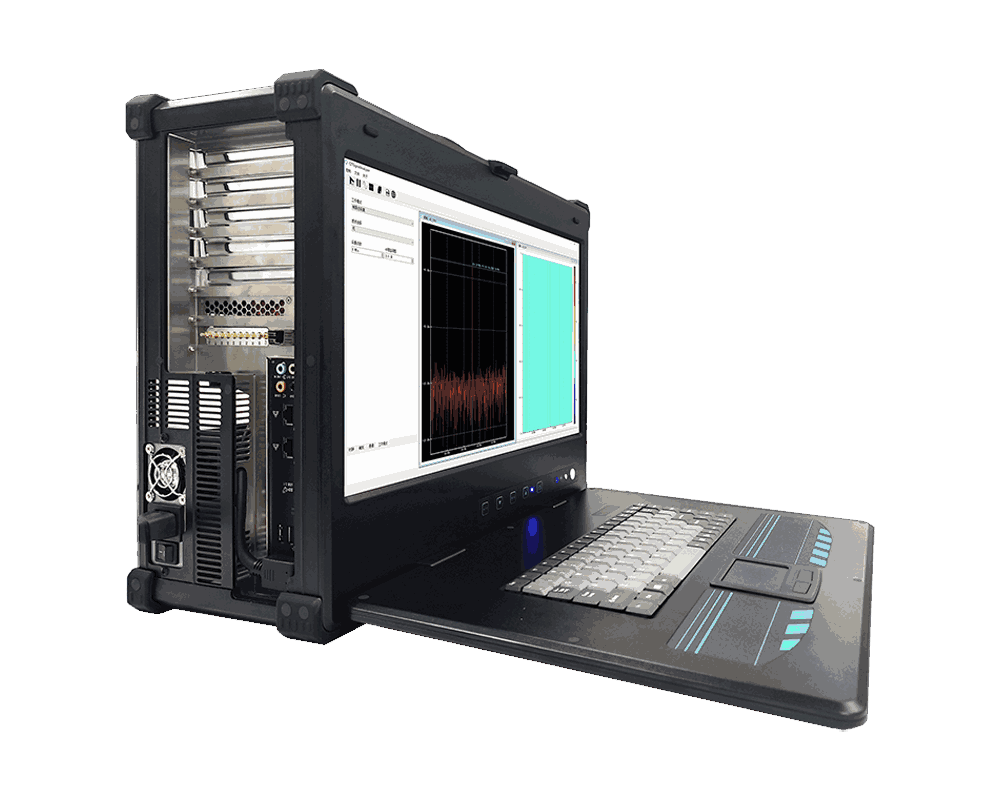

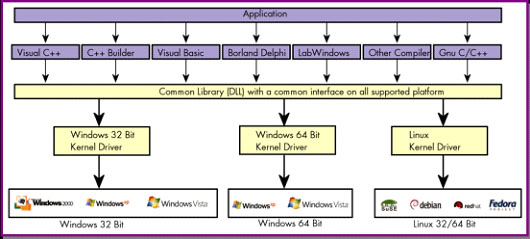

2.系統(tǒng)配套軟件:

系統(tǒng)軟件包括應(yīng)用軟件,,二次開發(fā)API函數(shù),,以及FPGA開發(fā)環(huán)境三部分,。

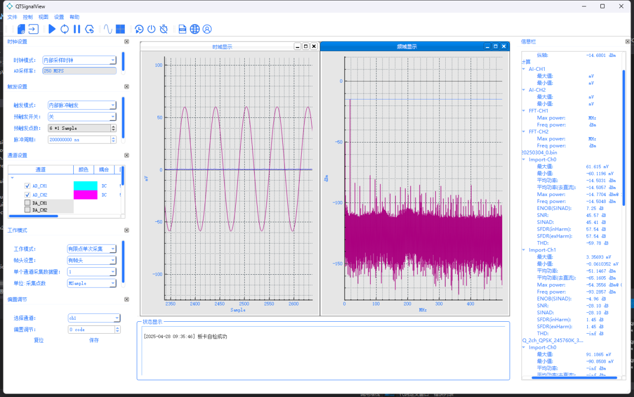

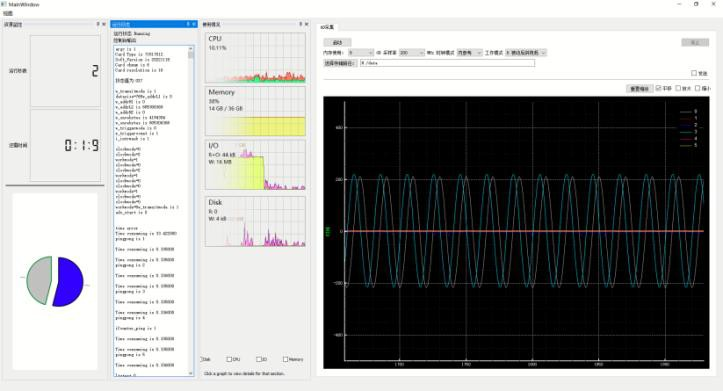

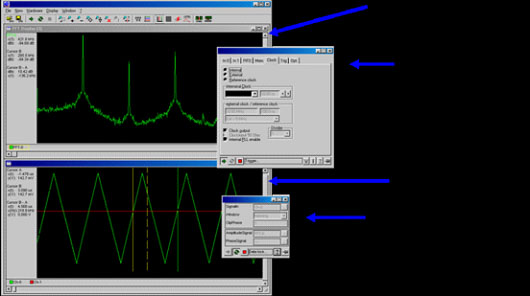

2.1應(yīng)用軟件

具有虛擬示波器功能,,方便設(shè)置硬件,讀取/保存數(shù)據(jù)以及波形顯示/頻譜分析功能,。

其功能和界面如下所示:

2.2二次開發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,,支持C/C++,labview以及Matlab環(huán)境下的二次程序開發(fā),。

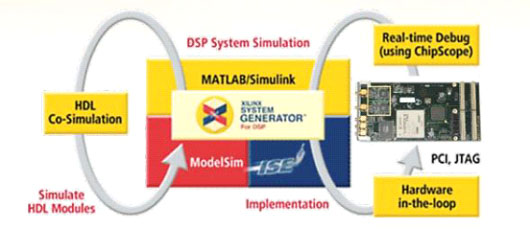

2.3FPGA開發(fā)環(huán)境:

我們提供采集模塊的全套FPGA開發(fā)工程,,全部基于VerilogHDL或VHDL開發(fā)環(huán)境。用戶邏輯只需要在目前已經(jīng)建立好的工程中加入自己的RTL代碼即可,。

同時提供Xilinx的systemgenerator同matlab/simulink接口工程和實例,。

-

SC800 nanoSynth集成6 GHz SMT合成器

輸出頻率范圍為25 MHz至6 GHz,平均輸出功率為+10 dBm

-

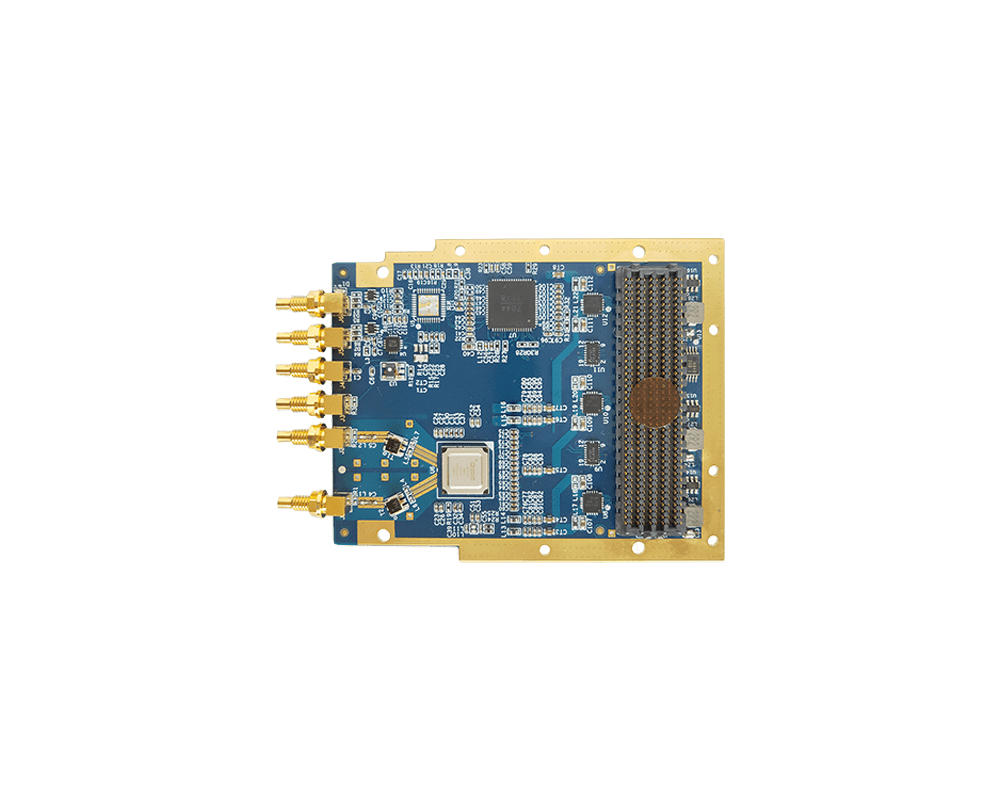

SC5412A ,SC5413A|IQ調(diào)制器

調(diào)制信號帶寬400MHz到6GHz,、直流160MHz基帶信號

-

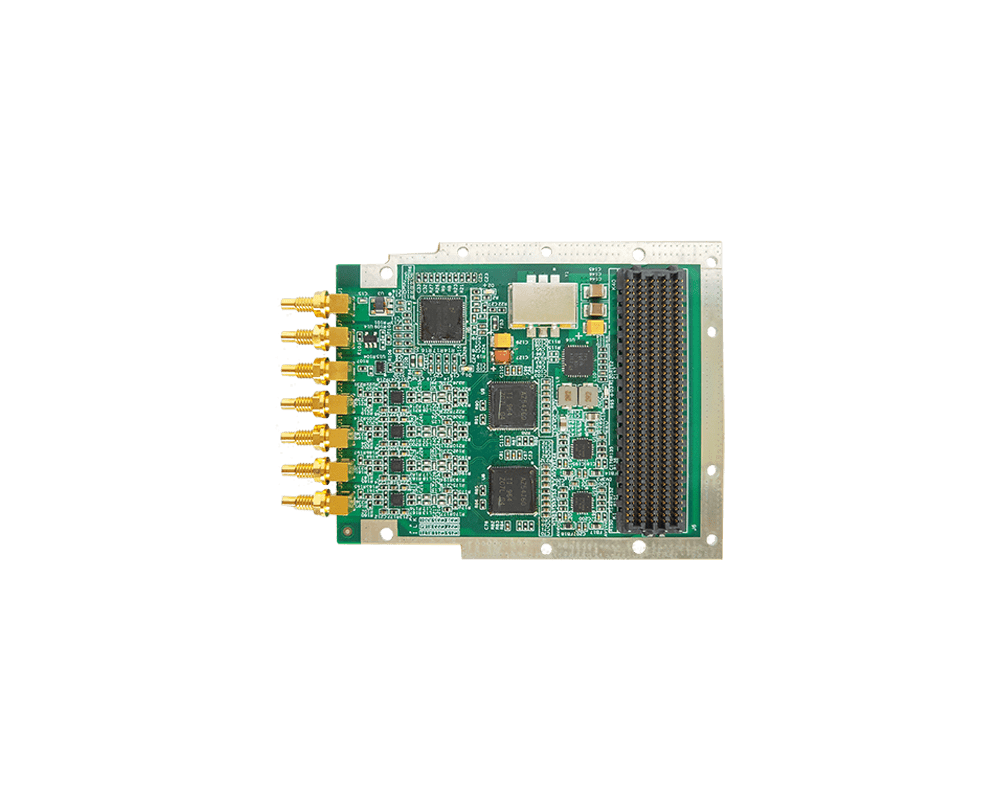

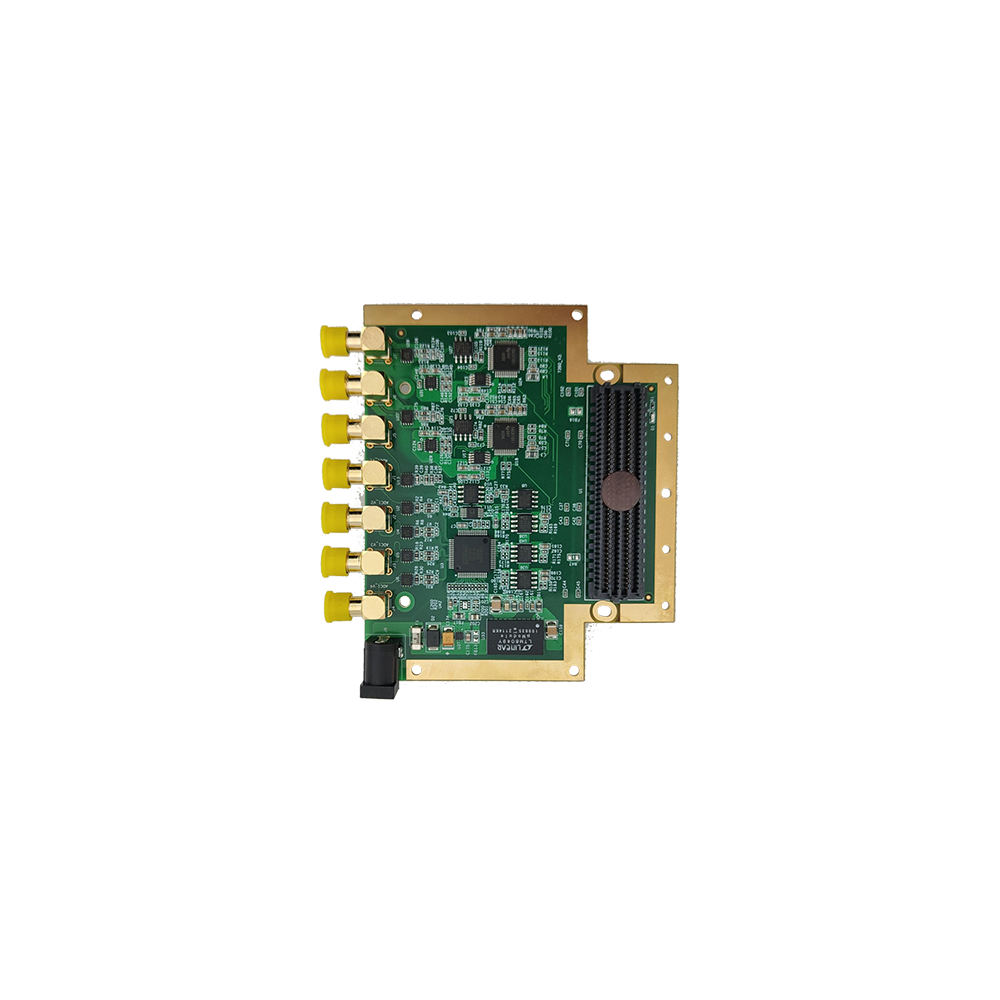

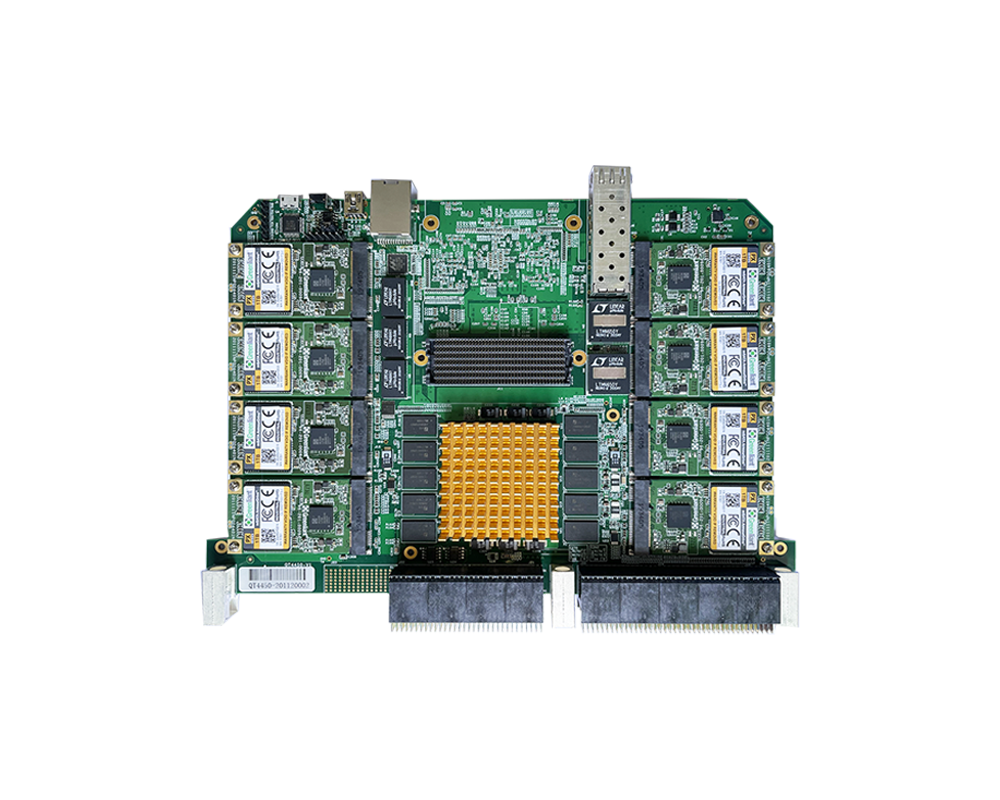

QT7131+AC-FMC AD子卡

4路14位 3.0/2.6/2.0GS/s A/D通道,,全功率模擬輸入帶寬(-3dB)可達9GHz

-

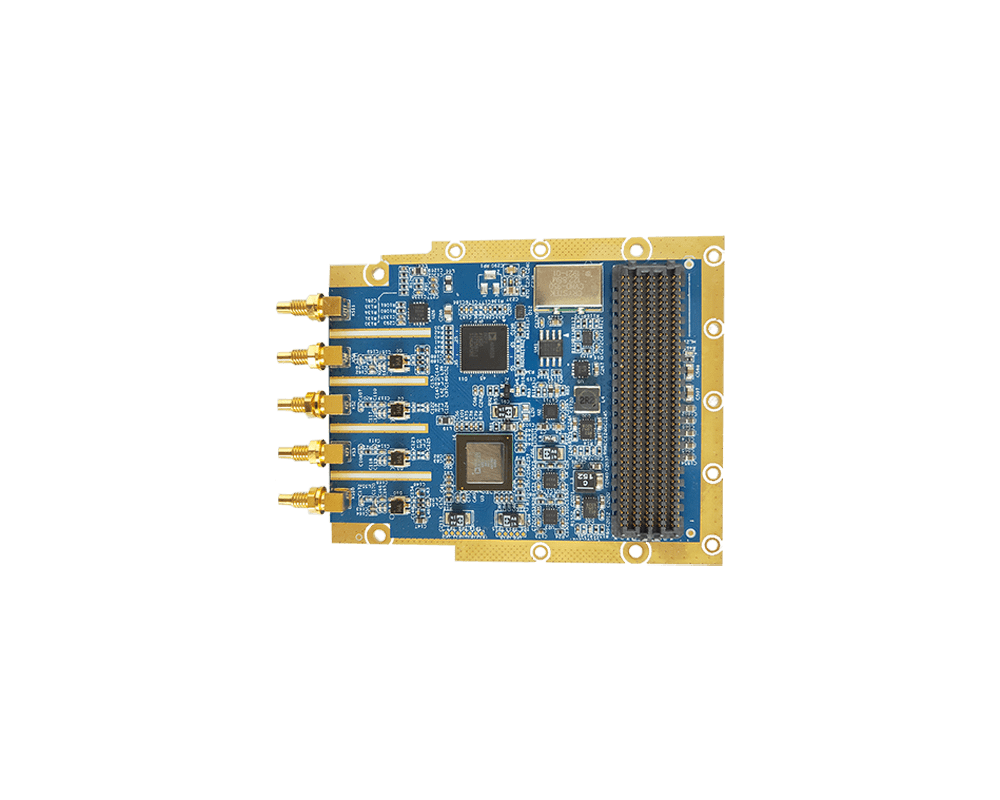

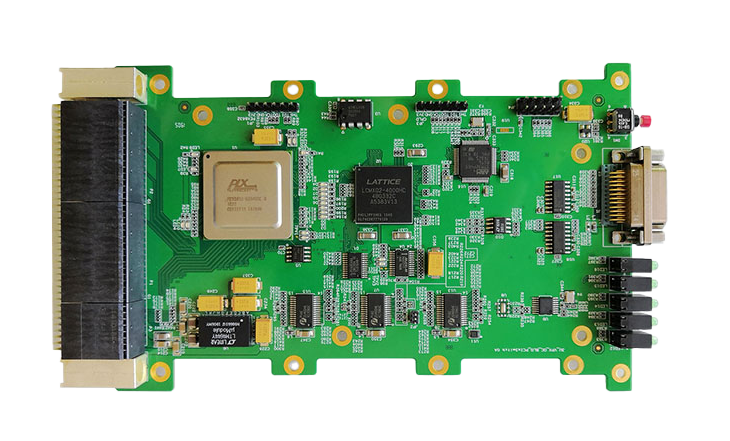

QT3310-3U VPX存儲板

標(biāo)準(zhǔn)3U VPX 導(dǎo)冷結(jié)構(gòu) 核心主控: 基于Xilinx K7 FPGA 的SoC 系統(tǒng) 高3.8GB/s 連續(xù)存儲速度 高達32TB 容量固態(tài)存儲