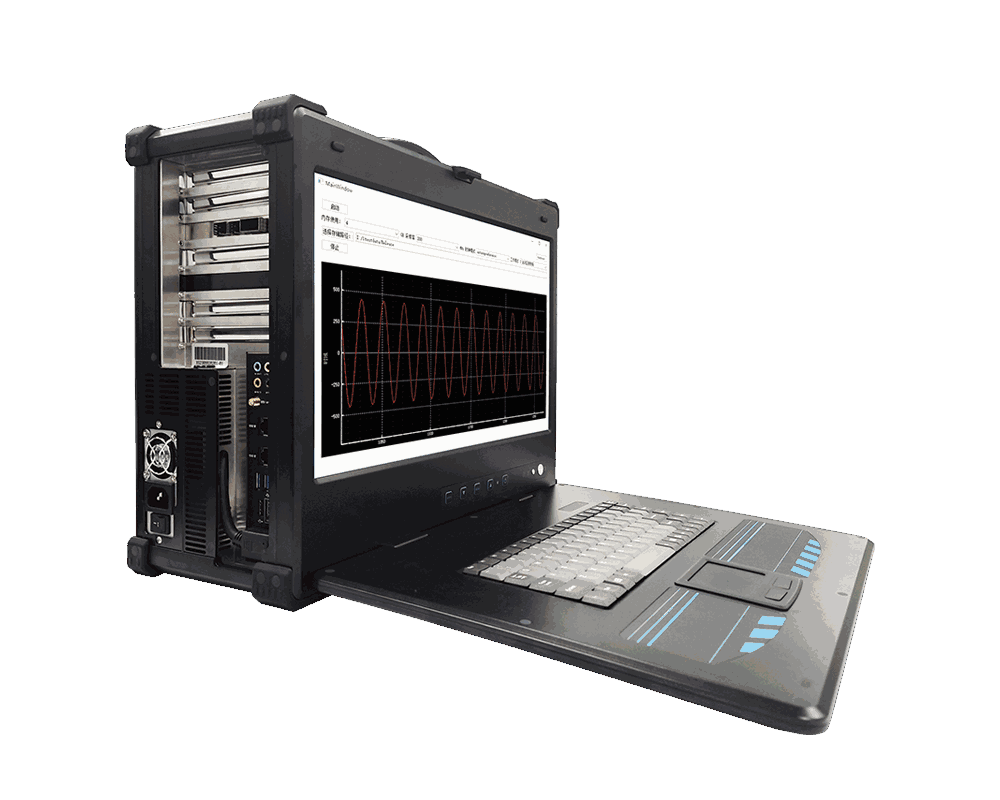

cPCI采集回放系統(tǒng)v3

cPCI/cPCIExpress接收/發(fā)送系統(tǒng)

接收/發(fā)送系統(tǒng)規(guī)格:

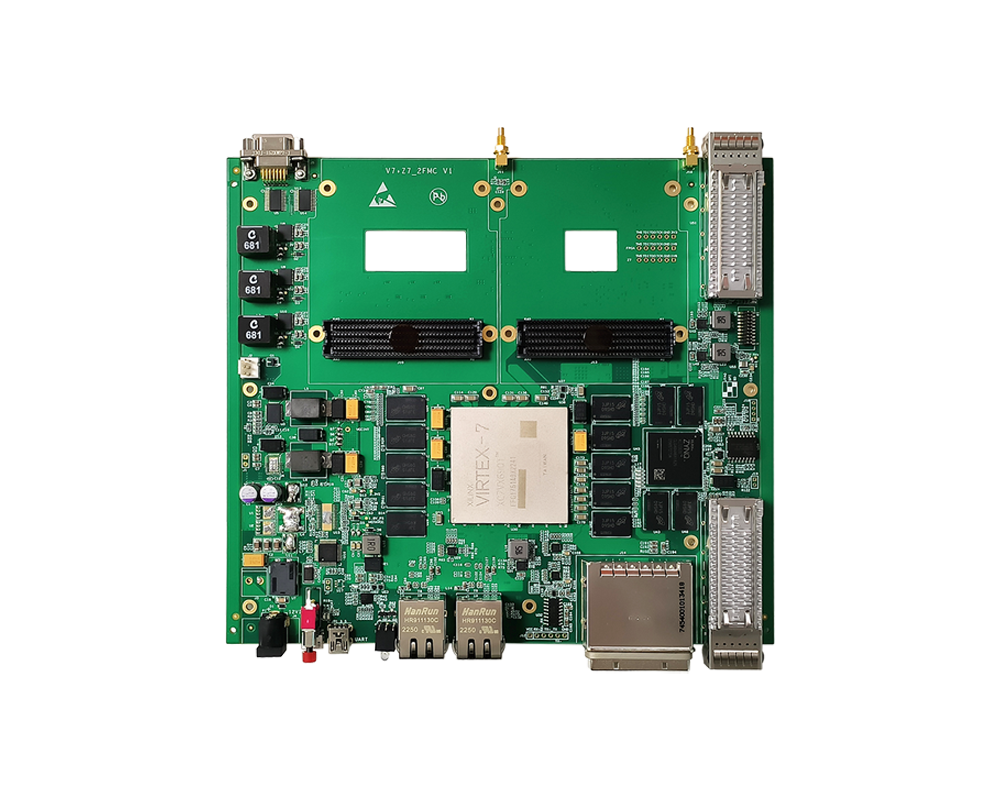

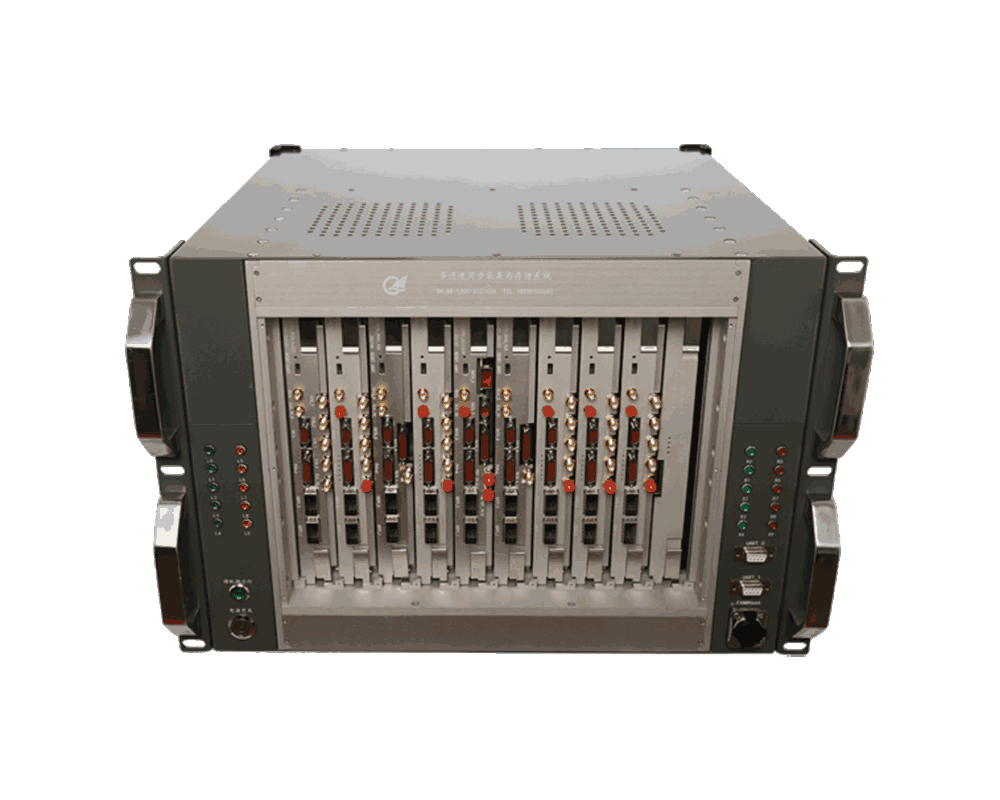

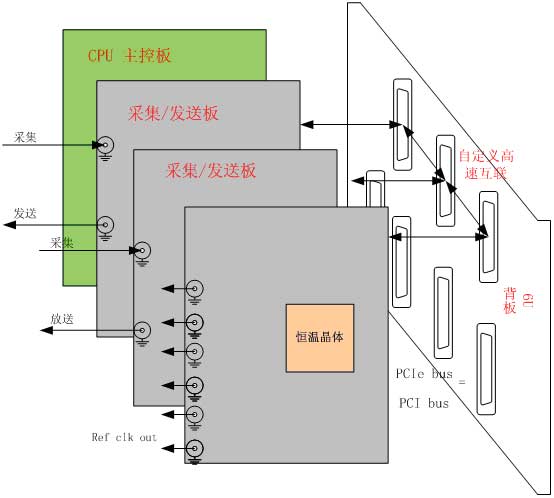

系統(tǒng)采用6U標(biāo)準(zhǔn)的cPCI/cPCIExpress架構(gòu),,包括如下幾個部分:

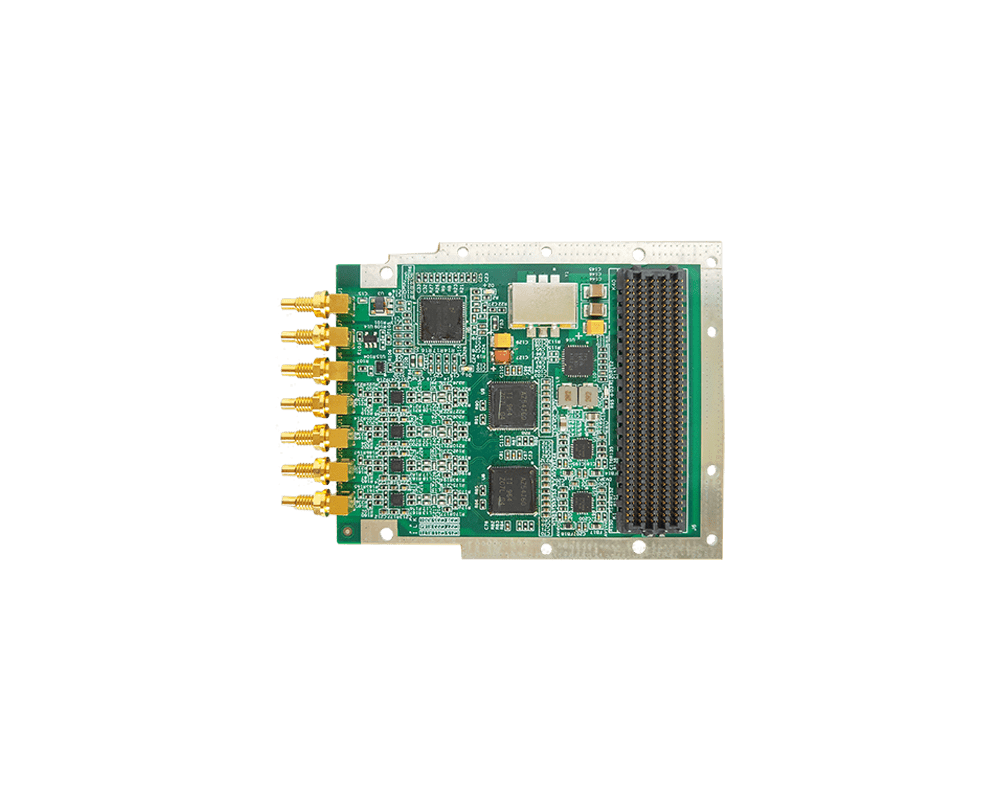

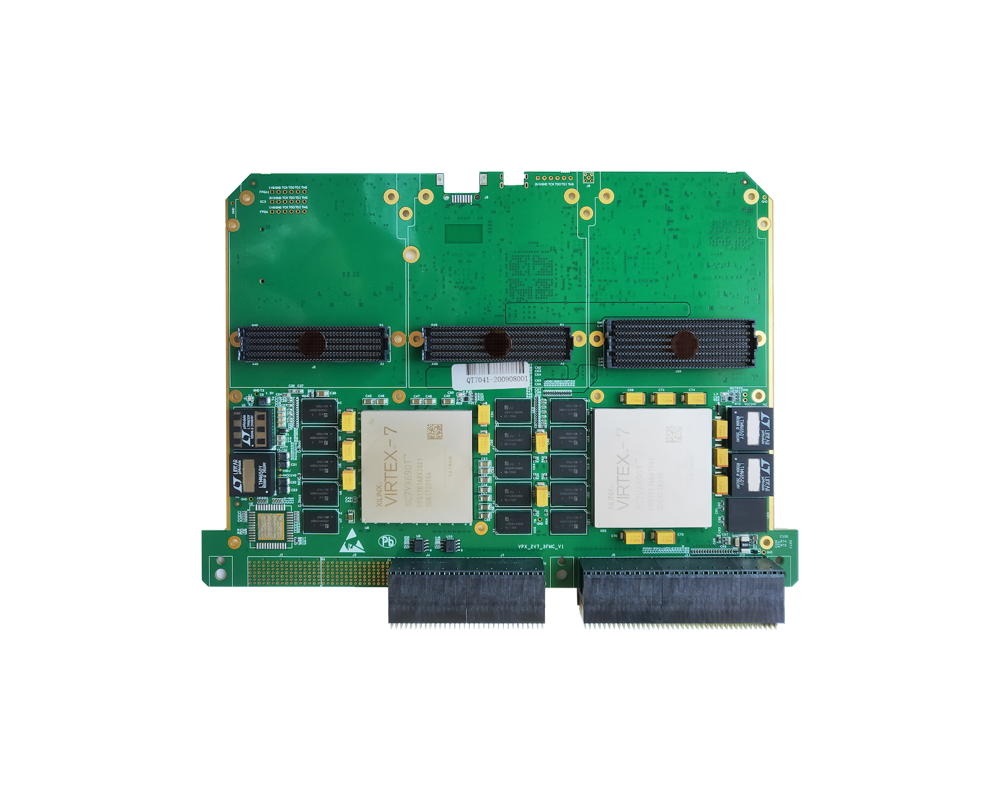

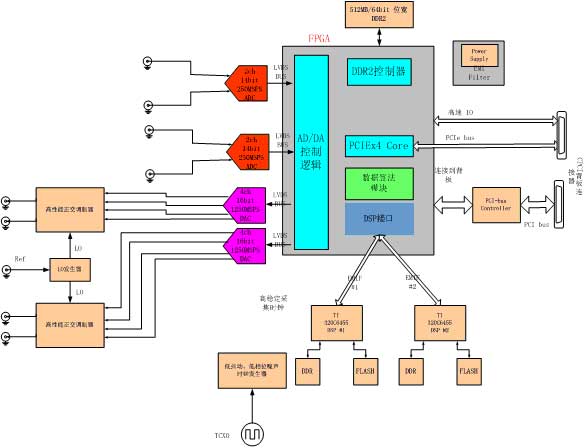

1.4通道14bit250MSPS采集模塊,采用TI的ADS42B49雙通道ADC,,部署兩塊該芯片,。

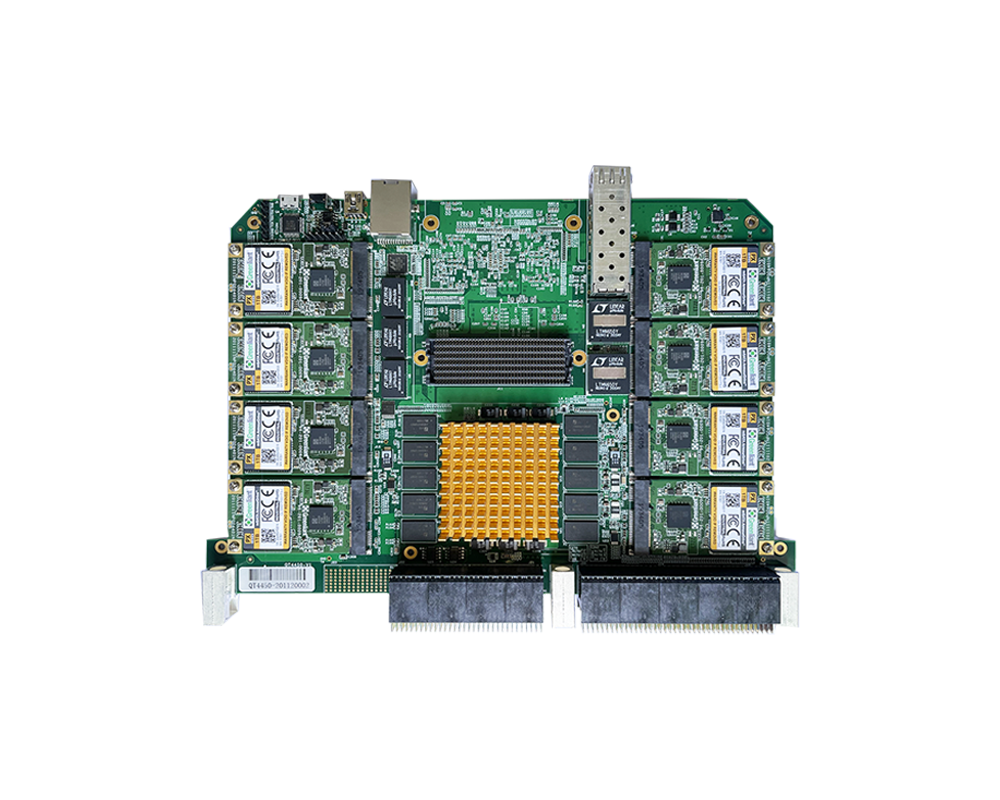

2.8通道16bit1250MSPSDAC模塊,,采用TI的DAC34H84芯片,部署兩塊該芯片,。

3.4通道正交調(diào)制模塊,,采用ADL5385,RF頻率范圍30MHz-2.2GHz,,板載高性能LO發(fā)生器。

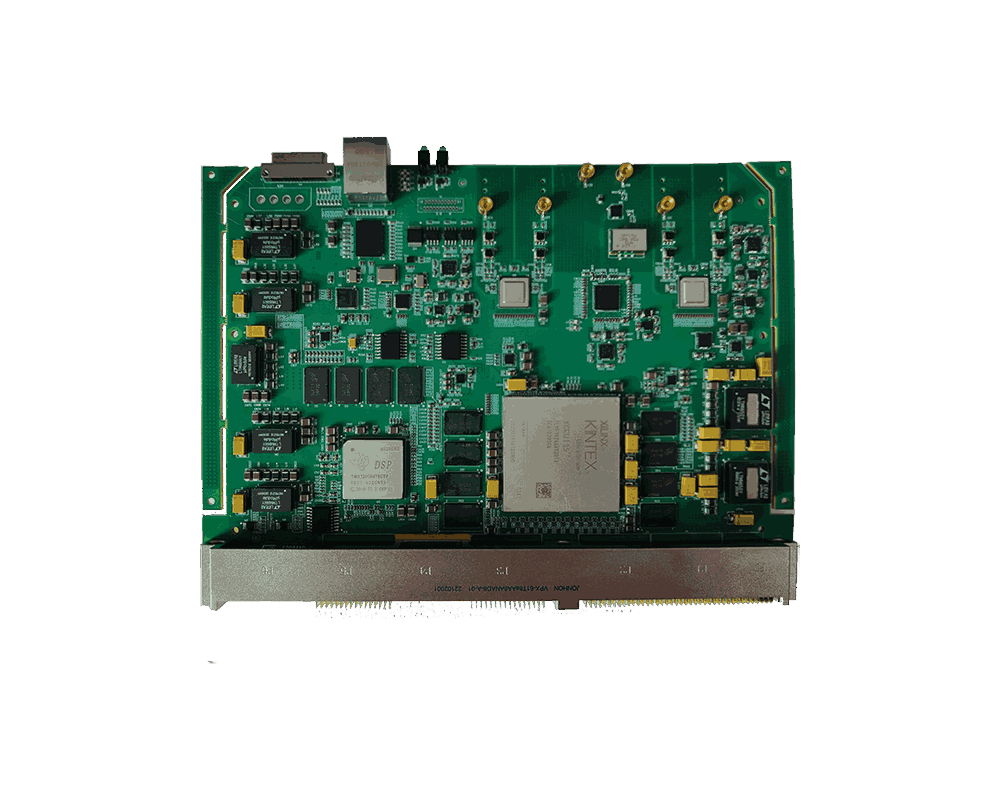

4.FPGA采用XilinxXC5VLX220TFPGA,。

5.板載512MB64位寬DDR2存儲器連接到FPGA,。

6.兩塊TI320C6455DSP,分別具有獨立的DDR2外存儲器和flash芯片,。

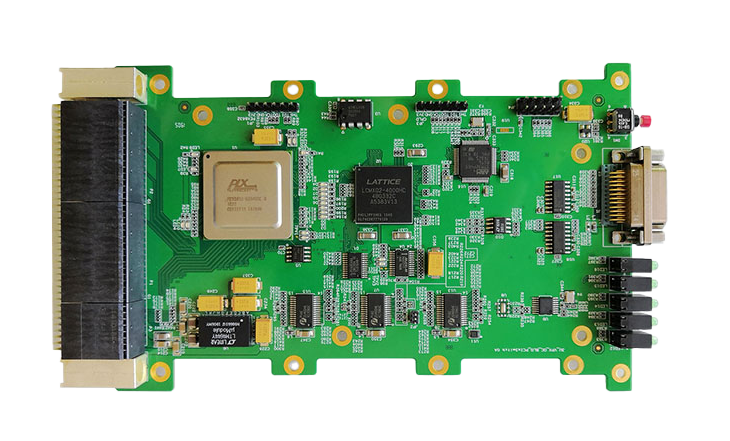

7.同時支持66MHz32bitPCI總線和PCIEx4總線,。

8.外置超低相噪恒溫晶體模塊,產(chǎn)生LO輸入?yún)⒖紩r鐘,。

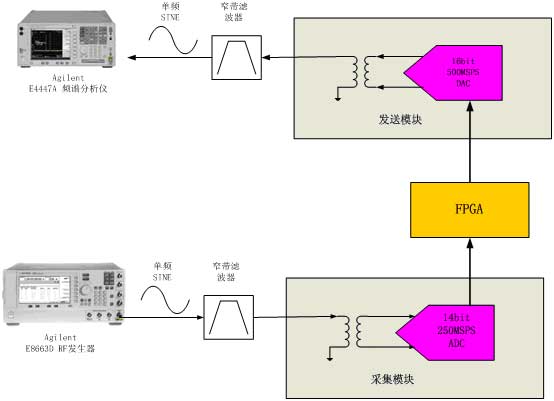

系統(tǒng)實現(xiàn)框圖如下:

該接收/發(fā)送以及CPU系統(tǒng)的組成模塊如下圖所示:

由于同時具有PCI總線和PCIE總線以,,該系統(tǒng)可以方便的CPU控制板和大容量存儲板進行連接,組成更靈活的系統(tǒng),。

采集/發(fā)送系統(tǒng):

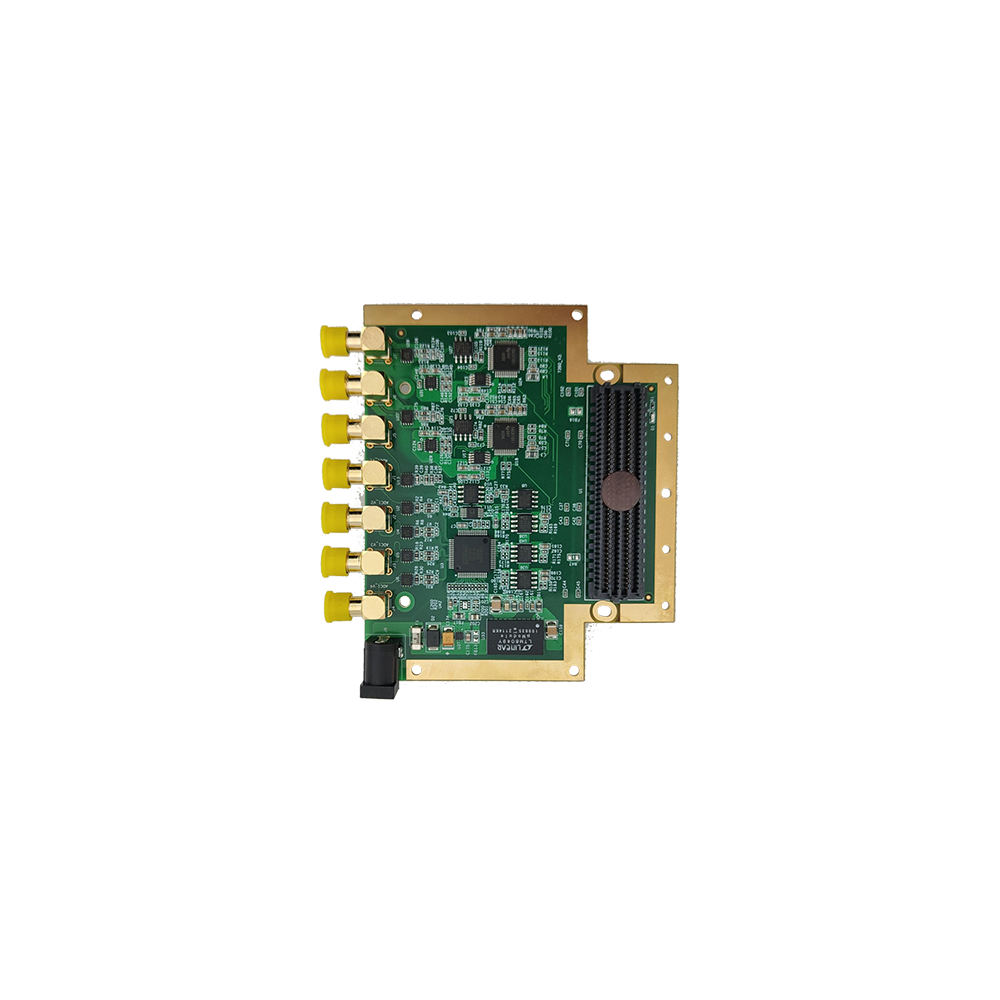

采集回放卡包括如下特性:

1.2通道14bit250MSPS采集,。50歐姆,AC耦合,,輸入幅度2Vpp,,700MHz帶寬。

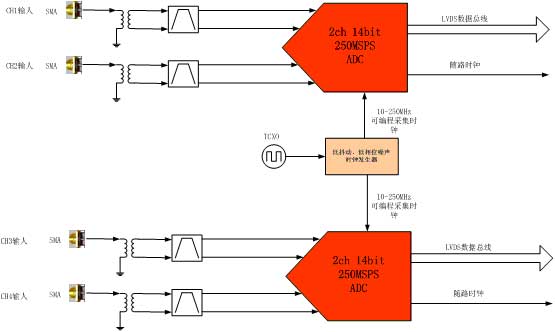

ADC采用TIADS42B49雙通道ADC:

信號由SMA接口輸入,,經(jīng)過變壓器藕合變成差分信號,;濾波器為可配置:直通、低通或帶通,,5階貝塞爾或巴特沃茲,。ADC所有輸出數(shù)據(jù)和隨路時鐘均連接到FPGA。采集時鐘通過高性能時鐘發(fā)生器產(chǎn)生,,采集頻率可在10MHz-250MHz范圍內(nèi)編程,。

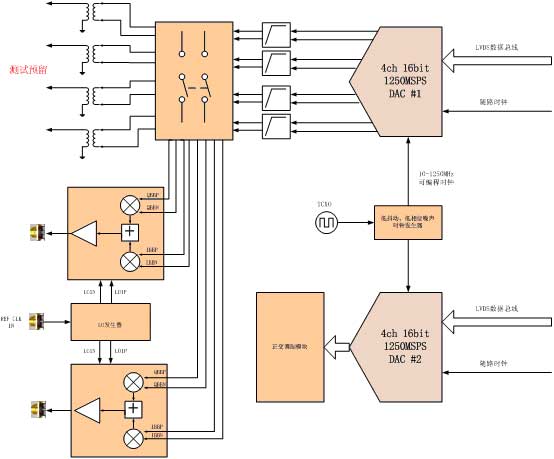

2.4通道16bit1250MSPSDAC,TI的DAC34H84芯片,,正交調(diào)制器采用ADL5385,。

DAC輸出采用1:4變壓器藕合,預(yù)留測試端口,,50歐姆負(fù)載下高輸出1Vpp電壓,。低通濾波器帶寬可以配置。DAC的采集時鐘通過高性能時鐘發(fā)生器產(chǎn)生,,采集頻率可在10MHz-1250MHz范圍內(nèi)編程,。

3.512MB本地緩存。

4.支持PCIEx4接口,。

5.支持PCI66M32bit接口

6.低抖動,、低相噪時鐘發(fā)生器,。

7.支持8對raidIO高速互聯(lián)接口,直接將數(shù)據(jù)通過背板傳輸?shù)酱鎯刂瓶ā?br />

8.可以多塊卡組成多通道同步工做模式,。

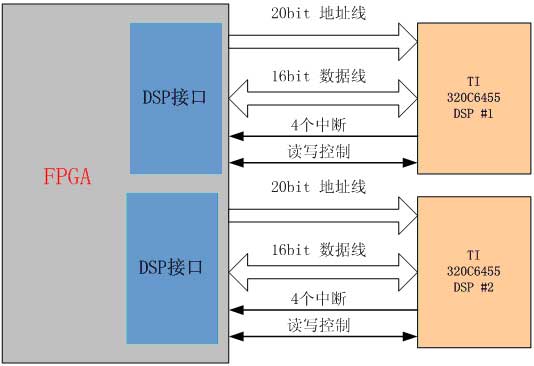

9.DSP同F(xiàn)PGA采用EMIF總線連接,連接關(guān)系如下:

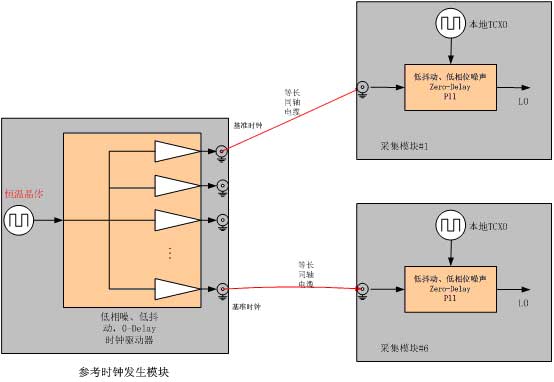

系統(tǒng)參考時鐘發(fā)生模塊:

本地采用高性能恒溫集體,,通過驅(qū)動器同時輸出6-8個參考時鐘輸出,。每個模塊采用zerodelayPLL,通過輸入?yún)⒖紩r鐘產(chǎn)生本地的LO給調(diào)制器,。

采集回放模塊性能指標(biāo)的保障:

對于采集回放模塊性能指標(biāo),,主要保障系統(tǒng)的信噪比大化。通過以下三方面來實現(xiàn):

1,、高精度的采集回放芯片,。采集回放模塊均采用TI的14bitADC和16bitDAC。支持較高噪聲擬制比和采集精度,,保障采集精度優(yōu)于信號本身的量化精度,。

2、高穩(wěn)定,,低噪聲的電源系統(tǒng),。

3、低抖動以及低噪聲的采集時鐘放生系統(tǒng),。采用有源溫度補償VCXO,,analogdevice的時鐘管理芯片,保證了采集系統(tǒng)的高穩(wěn)定度和低抖動,。

關(guān)于采集/回放的性能測試:

采集回放系統(tǒng)性能測試方案分為兩部分:

1.測試采集/回放系統(tǒng)本身的性能,,如信噪比SNR,THD以及ENOB等測試項目,。其測試方法如下:

ADC模塊的測試:

使用AgilentE8663DRF信號發(fā)生器,,主要發(fā)生單頻的sine信號,通過窄帶濾波器,,保證sine的“純凈”,。信號幅度為+/-1V輸出,保證ADC輸入的滿幅度,。

信號通過ADC采集后進入PC并存儲,,通過測試軟件進行數(shù)據(jù)處理。

關(guān)于ADC采集數(shù)據(jù)的處理及計算方法:

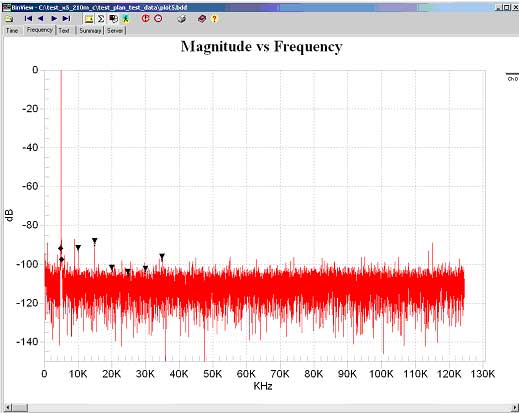

Data輸入可以選取2048個點,,同hanningwindow進行卷積,,防止矩形窗引起的Gibbs現(xiàn)象。

卷積后的信號進行FFT,,得到頻譜數(shù)據(jù),。這是為了測試數(shù)據(jù)的準(zhǔn)確性,,可以多采集幾次進行譜平均,得到更準(zhǔn)確的譜數(shù)據(jù),。

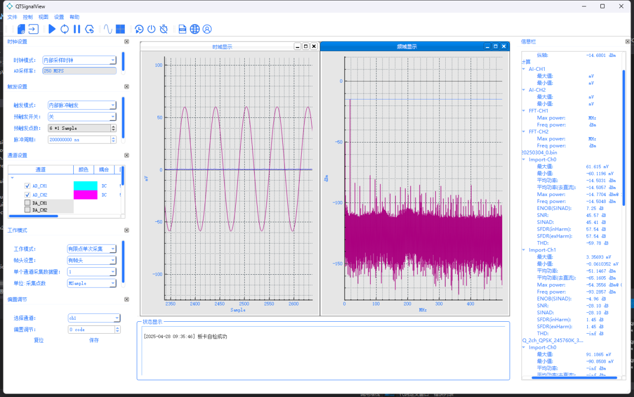

上圖為14bitADC在250Msps采樣率下采集單頻信號的頻譜,。

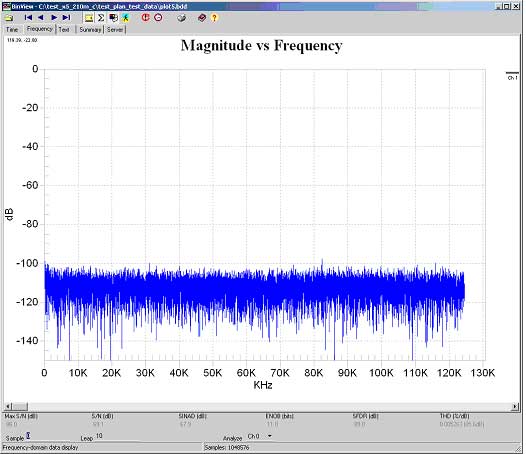

上圖為ADC輸入底噪聲頻譜。

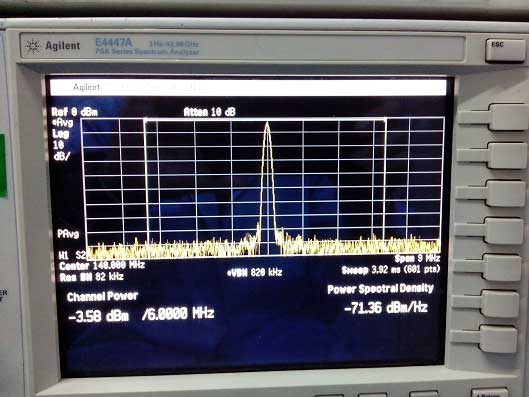

DAC的性能測試

DAC在220MHz時鐘下(采用mixfreg算法,,相當(dāng)于110MHz時鐘DAC工作在1.25Fs,第二來奎斯特區(qū)域)產(chǎn)生140MHz中頻的測試結(jié)果:

噪聲密度在-90dBm,。

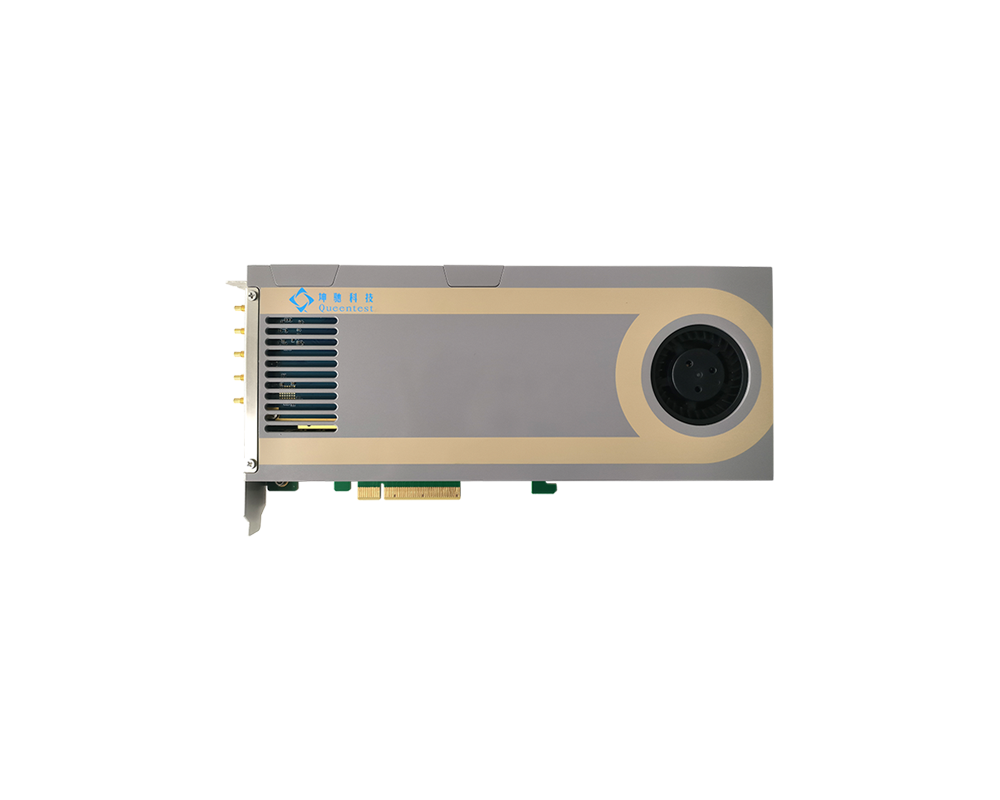

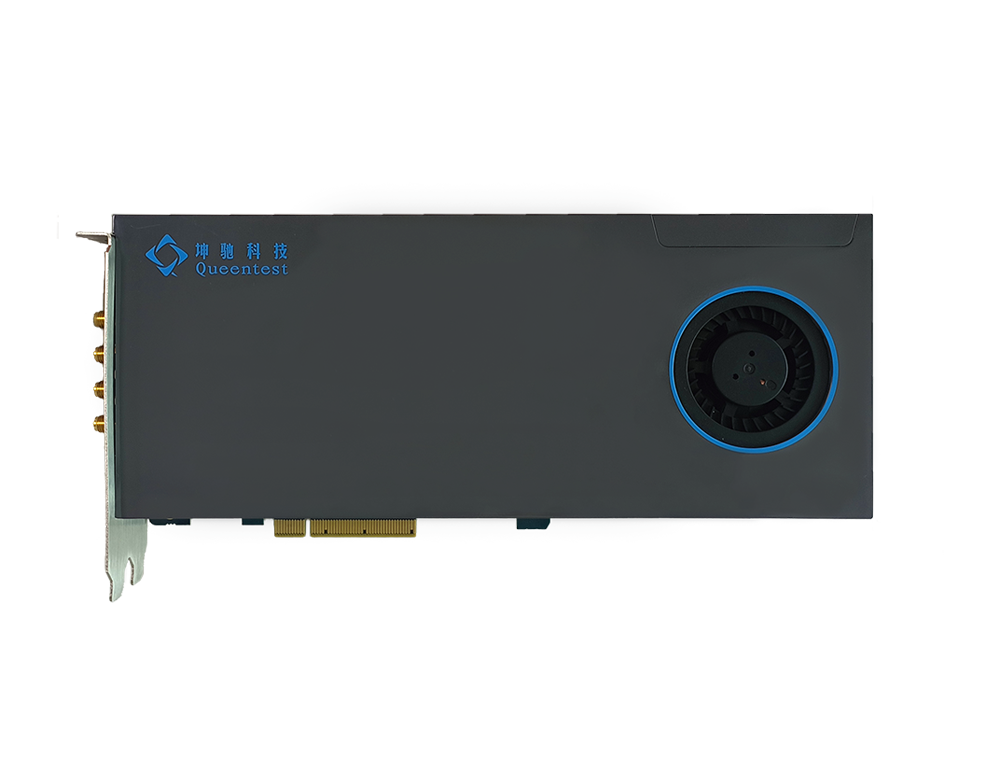

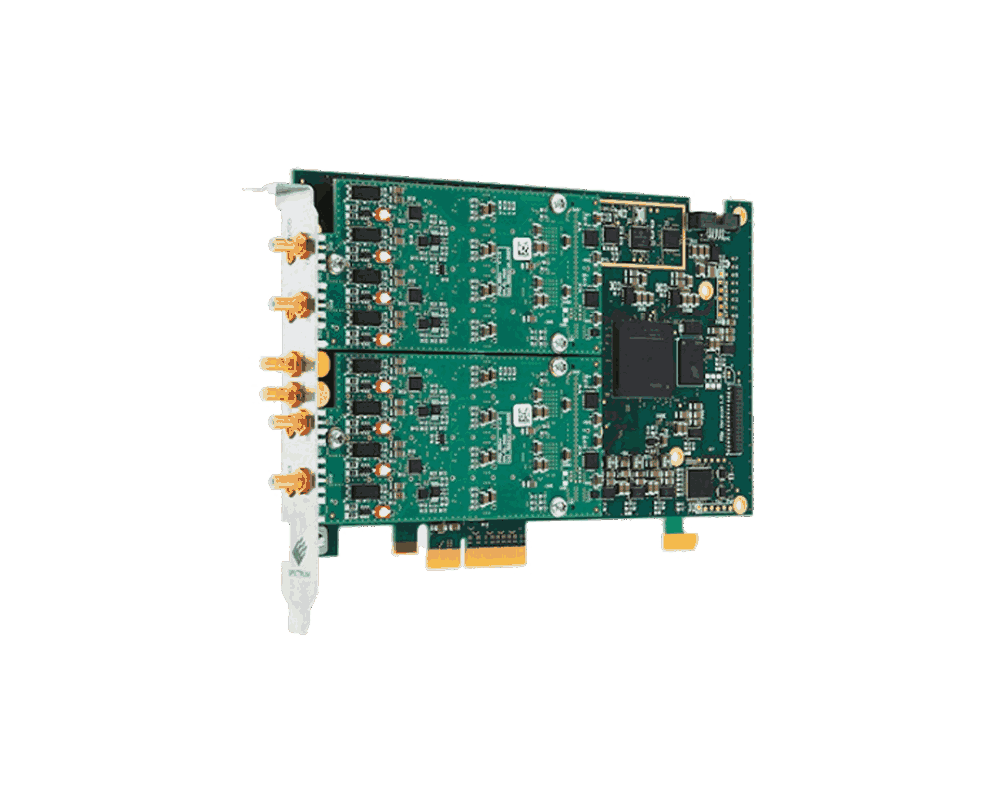

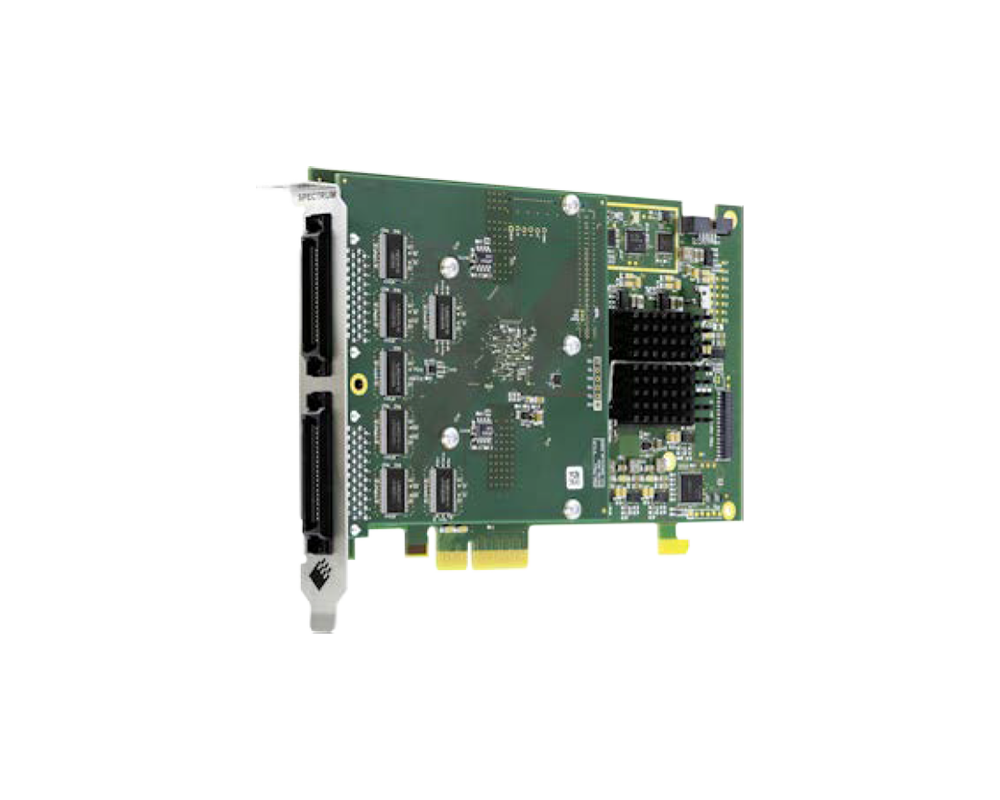

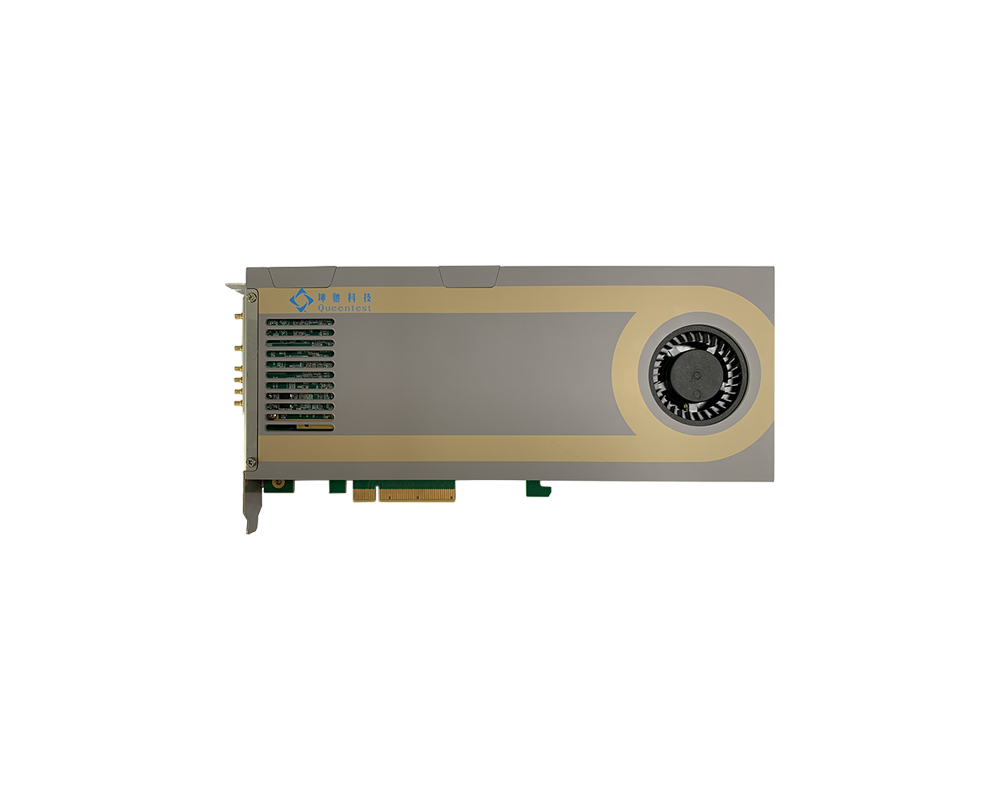

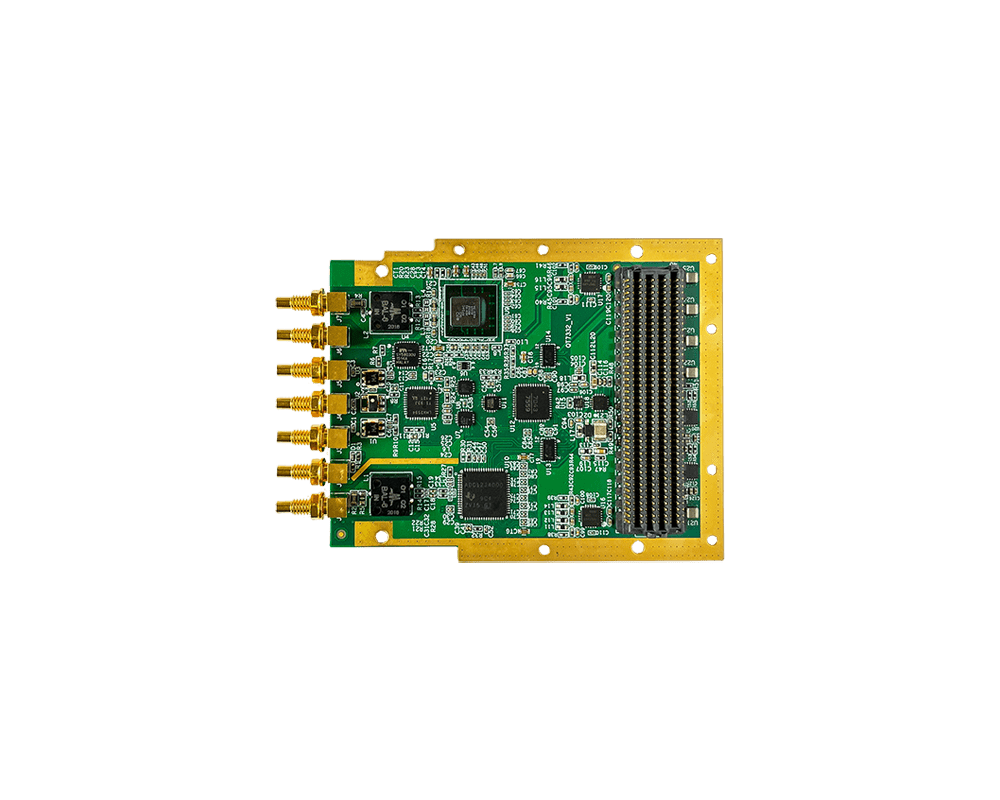

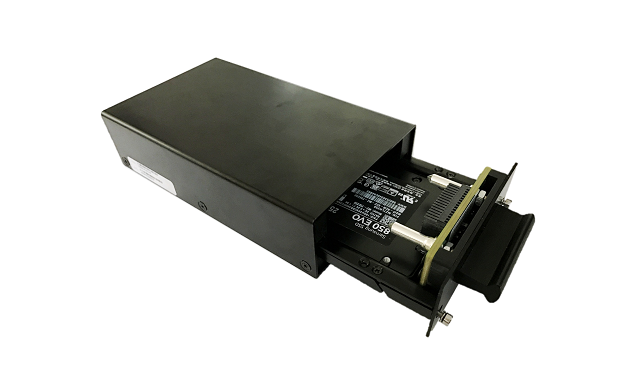

采集板卡參考外觀圖如下:

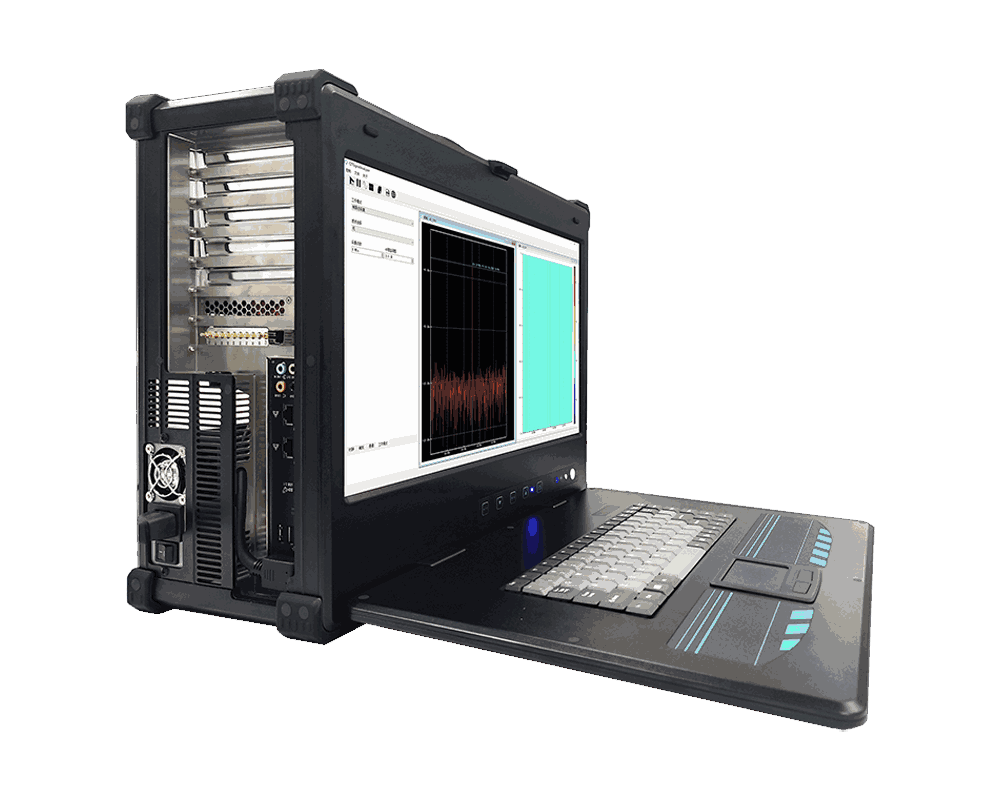

系統(tǒng)配套軟件:

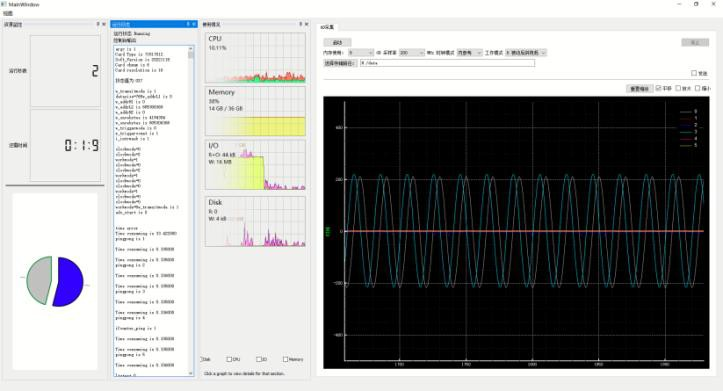

系統(tǒng)軟件包括應(yīng)用軟件,二次開發(fā)API函數(shù),,以及FPGA開發(fā)環(huán)境三部分,。

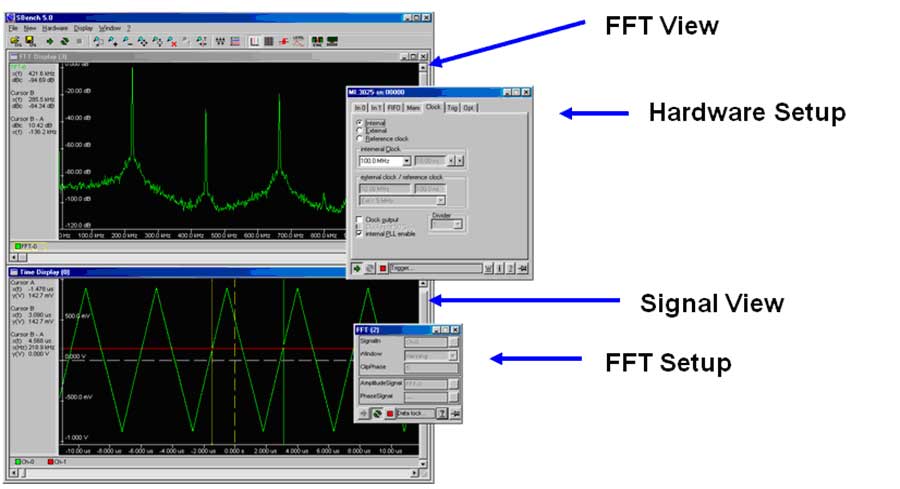

1.應(yīng)用軟件:具有虛擬示波器功能,方便設(shè)置硬件,,讀取/保存數(shù)據(jù)以及波形顯示/頻譜分析功能,。

其功能和界面如下所示:

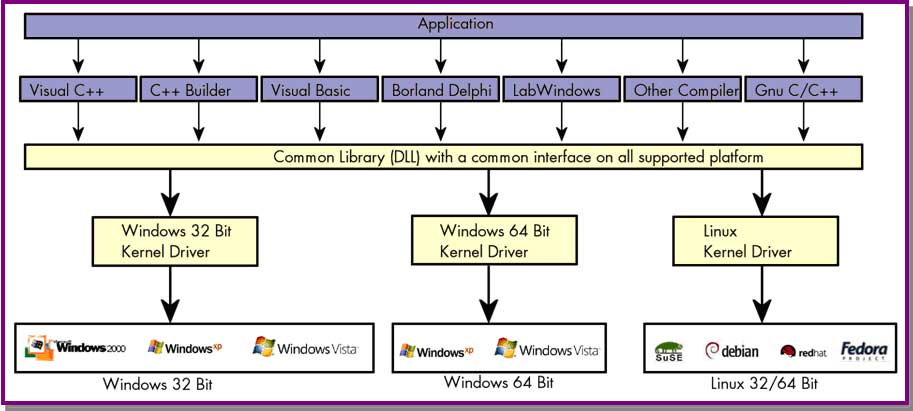

2.二次開發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,支持C/C++,,labview以及Matlab環(huán)境下的二次程序開發(fā),。

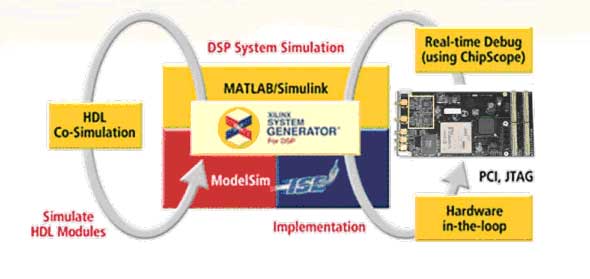

3.FPGA開發(fā)環(huán)境:

采集模塊具備基于VerilogHDL或VHDL的FPGA開發(fā)環(huán)境。用戶邏輯只需要在目前已經(jīng)建立好的工程中加入自己的RTL代碼即可,。

同時提供Xilinx的systemgenerator同matlab/simulink接口工程和實例,。

-

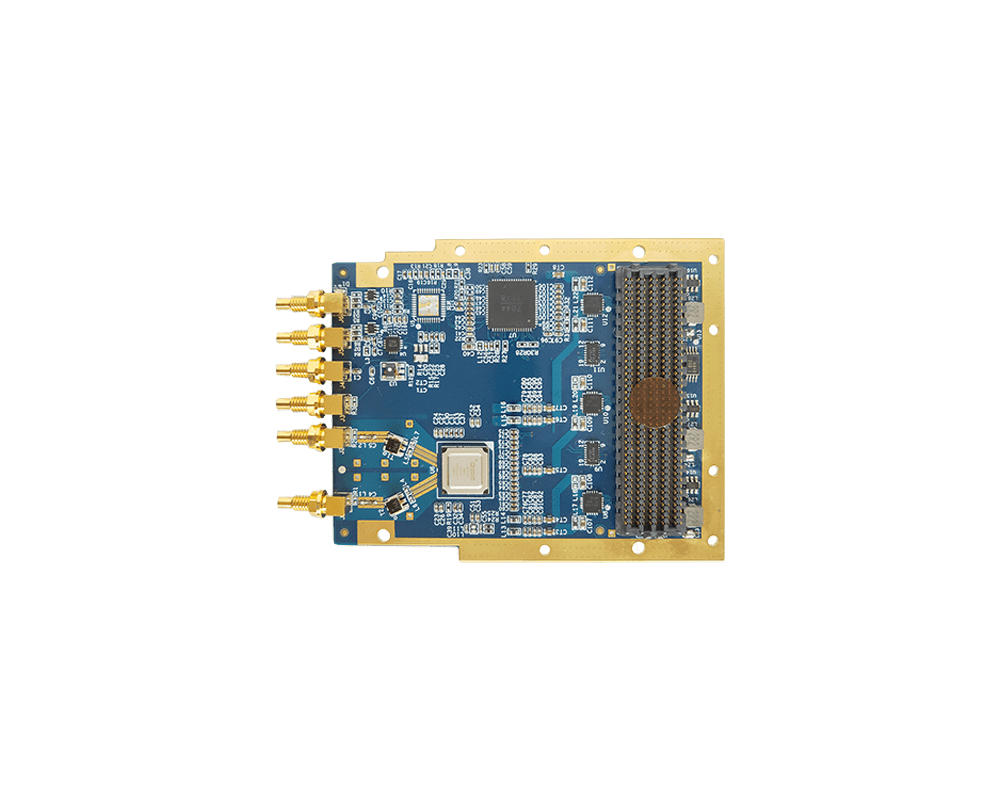

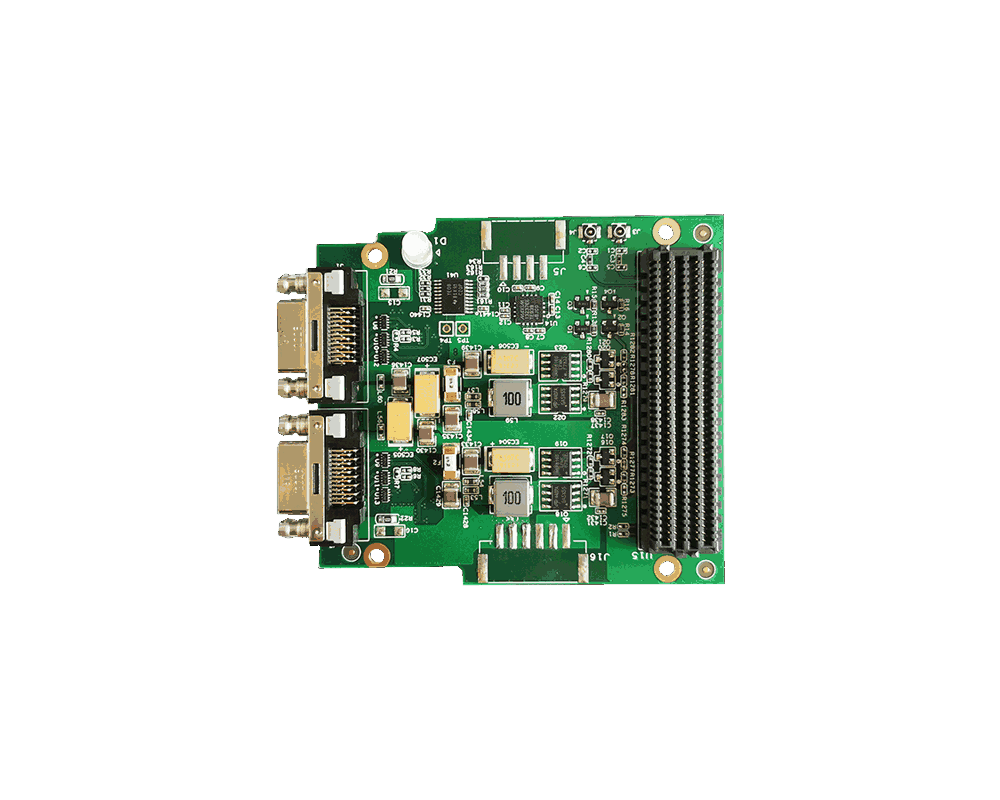

QT7332-FMC AD/DA子卡

1通道,12bit,,4GS/s,,ADC和1通道,14bit,,12.8GS/s,,DAC

-

QTC2000S-圖像采集記錄儀

SDI 接入,持續(xù)存儲最低速率 800MB/s,,最高容量 4TB

-

VPX-FT6287

坤馳科技VPX-FT6287是一款6U VPX主控板,,采用FT2000+/64處理器平臺,板貼128GB內(nèi)存,,板上可擴展1個M.2 NVME接口,,前面板支持2路10G光口,板上可選國產(chǎn)PCIE擴展橋片

-

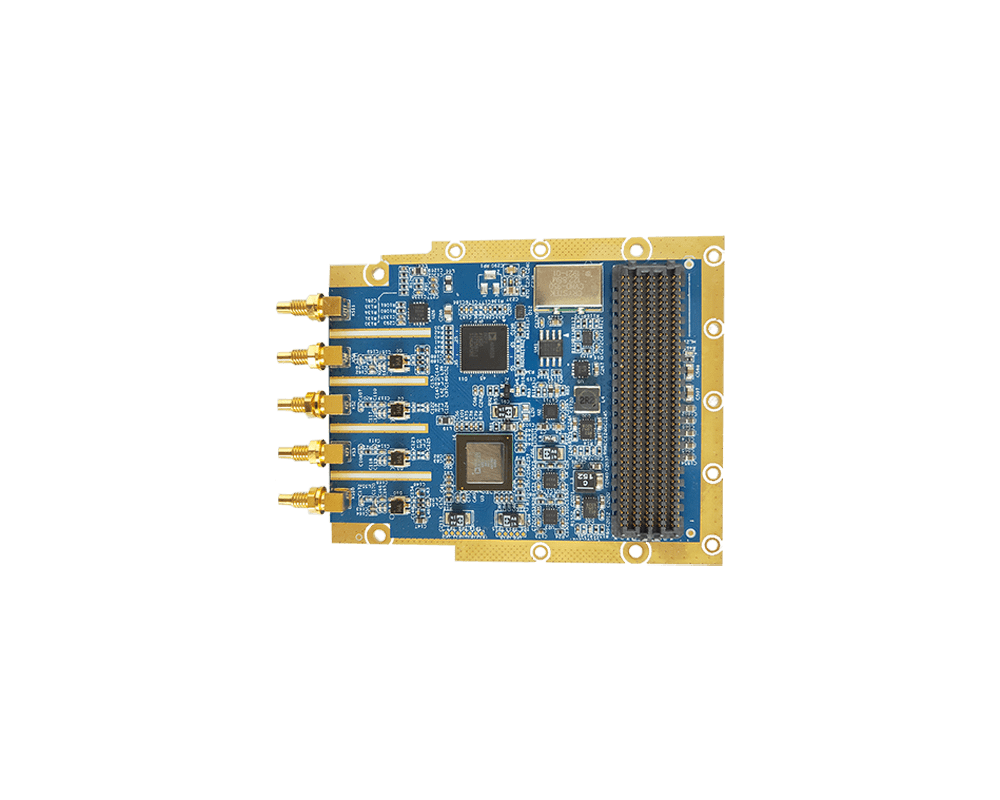

SDR14TX-PXIe總線直流耦合采集卡

分辨率14位,;輸出信號范圍0.5至2 Vpp1),;輸出通道2;更新率 2 GHz,;1 GByte板載存儲