熱搜關(guān)鍵詞: 高速AD卡FMC子卡高速數(shù)據(jù)采集系統(tǒng)軟件無線電平臺VPX高速數(shù)據(jù)采集卡高速信號采集卡PCIe高速數(shù)據(jù)采集卡RFSOC

碼上聯(lián)系

碼上聯(lián)系

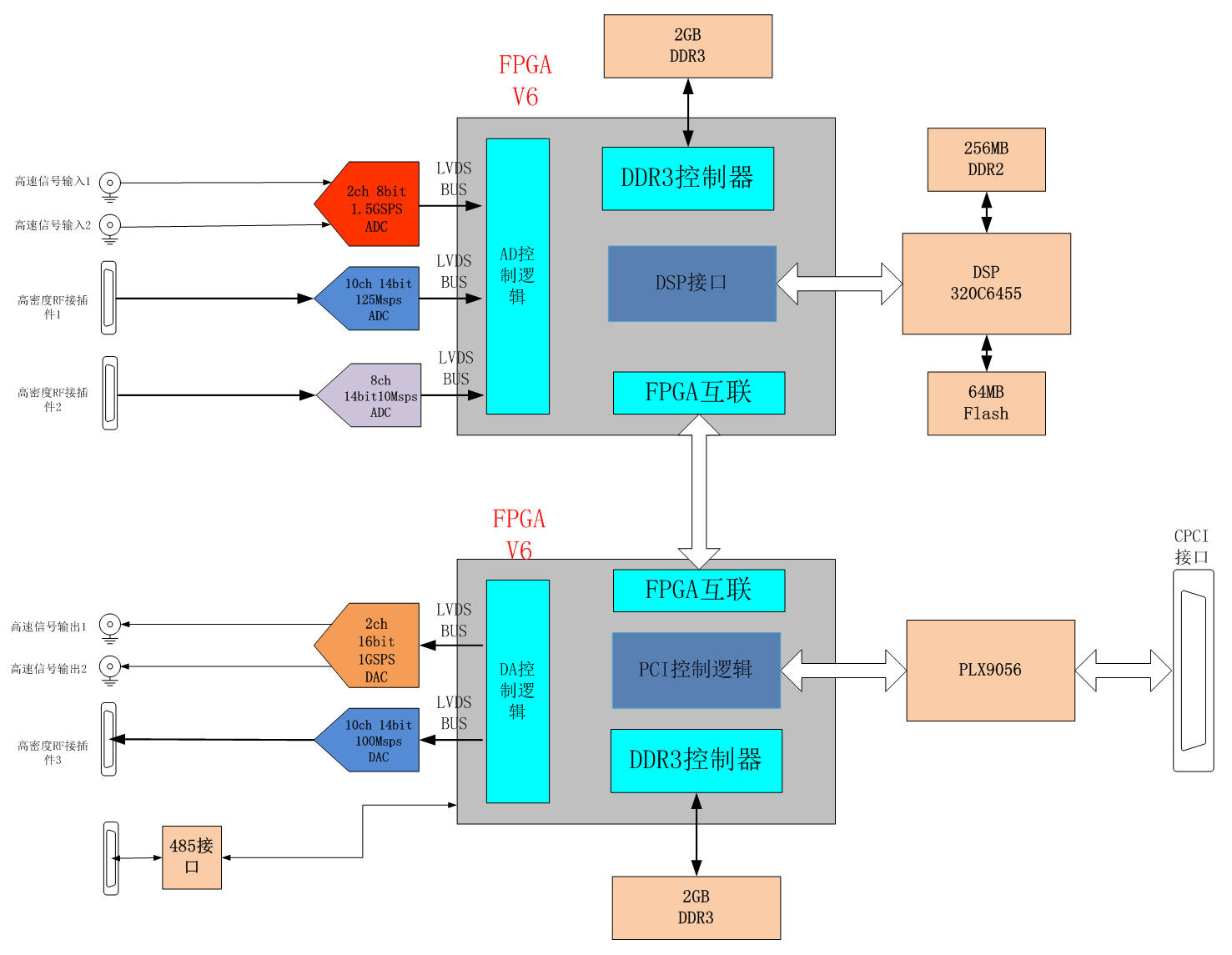

接收/發(fā)送系統(tǒng)規(guī)格:

系統(tǒng)采用6U 標(biāo)準(zhǔn)的CPCI 架構(gòu),,包括如下幾個部分:

1.2通道 8bit 1.5GSPS 采集模塊。

2.10通道 14bit 125MSPS ADC模塊,。

3.8通道14bit 10MSPS ADC模塊,。

4.2通道 14bit 1GSPS DAC模塊,。

5.10通道 14bit 125MSPS DAC模塊。

6.FPGA采用 2塊 Xilinx XC6VLX315T FPGA,。

7.每塊FPGA部署 2GB 64位寬 DDR3 存儲器,,總共4GB 板載內(nèi)存。

8.?dāng)U展TI 320C6455 DSP,,分別具有獨立的DDR2外存儲器和flash 芯片,。

9.采用PLX9056接口芯片,支持66MHz 32bit PCI總線,。

10.6個485接口,,IO方向可控制。

11.標(biāo)準(zhǔn)6U CPCI板卡,,3槽寬度

系統(tǒng)實現(xiàn)框圖如下:

采集模塊

2通道高速采集,。SMA輸入,單端50歐姆,,AC耦合,,輸入幅度2Vpp,1000MHz帶寬,。信號由SMA接口輸入,,經(jīng)過變壓器藕合變成差分信號;濾波器為可配置:直通,、低 通或帶通,,5階貝塞爾或巴特沃茲。ADC所有輸出數(shù)據(jù)和隨路時鐘均連接到FPGA,。采集時鐘通過高性能時鐘發(fā)生器產(chǎn)生,,采集頻率可在10MHz-1500MHz范圍內(nèi)編程。

高速采集芯片采用TI公司的ADC08D1520芯片,,支持雙通道1.5GSPS采樣,。

ADC性能指標(biāo):

3. 10通道采集采用14bit 125Msps,,8通道采集采用14bit 10Msps,均為直流藕合,,50歐姆輸入阻抗,,高密度接插件

14bit 125Msps ADC采用Linear公司的LTM9012芯片。該芯片集成4通道14bit 125Msps ADC

8通道采集采用linear 公司LTM9006 芯片,。單個模塊集成8通道14bit 25Msps ADC,,本系統(tǒng)工作在10Msps采樣率上

4. 2通道高速DAC,。SMA輸出,單端50歐姆,,AC耦合,,輸出幅度1Vpp,1000MHz帶寬,。

高速DAC采用TI公司的DAC5681芯片,,16bit 1Gsps 采樣率。

5. 10通道DAC采用14bit 100Msps,,均為直流藕合,,50歐姆輸出阻抗,高密度接插件

該DAC采用TI的DAC290414bit 125Msps 芯片

6. DSP同F(xiàn)PGA采用EMIF總線連接,。

DSP芯片為TI的TMS320C6455,,有如下性能:

工作頻率為1.2GHz;

計算能力9600MIPS,;

32bit位寬 256MB DDR2 內(nèi)存,,數(shù)據(jù)頻率533MHz;

64MB 程序FLASH

通過高速同步EMIF總線同F(xiàn)PGA連接,。

7. FPGA模塊:采用兩塊XILINX 的XC6VLX315T FPGA并聯(lián),ADC通道和DAC通道分別由單獨的FPGA控制,,

每塊FPGA具有獨自的DDR3存儲單元,,外接64bit 位寬 2GB DDR3芯片,數(shù)據(jù)頻率1066MHz,,提供64Gbps的數(shù)據(jù)讀寫帶寬,。

FPGA間采用96對高速LVDS互聯(lián)。

8. 模擬輸入輸出:

模擬輸入輸出均采用SMA接口,,總共占用3個6U槽位:

1號槽位:高速ADDA,4 SMA,;485接口

2號槽位:18個SMA,,中速和低速ADC接口

3號槽位:10個SMA,中速DAC接口

低速,、中速模擬接口采用內(nèi)部高密度接插件和射頻電纜連接,。

應(yīng)用:

算法仿真與驗證、

了解更多詳情,,可以撥打熱線咨詢400-000-4026