8通道數(shù)據(jù)采集回放系統(tǒng)

一、方案

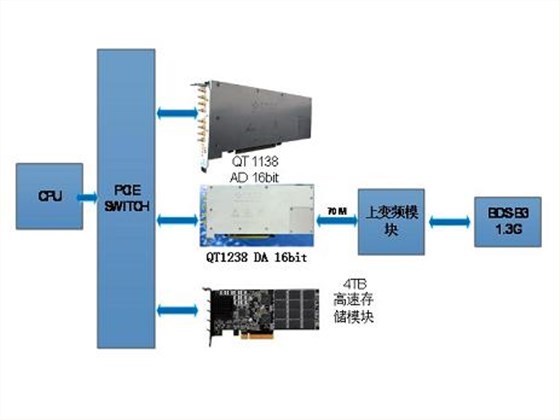

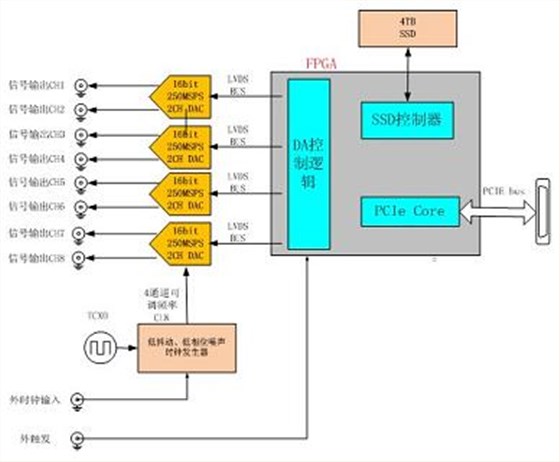

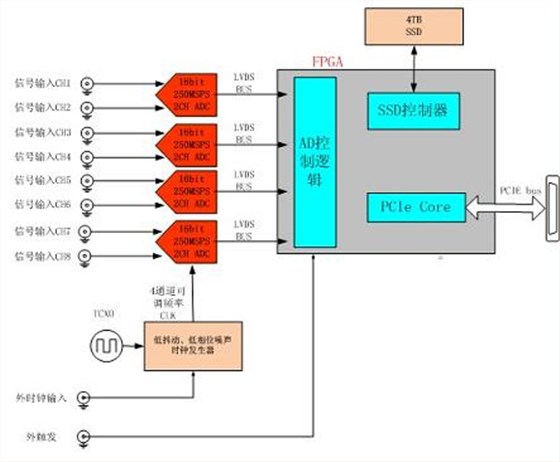

采集系統(tǒng)由工控計(jì)算機(jī),、模數(shù)AD轉(zhuǎn)換系統(tǒng)QT1138,,數(shù)模DA轉(zhuǎn)換系統(tǒng)QT1238、SSD存儲(chǔ)器,,上變頻等模塊組成,;各個(gè)模塊集成在一臺(tái)工控機(jī)箱中。其集成工作原理見(jiàn)下圖:

1.1PCIE采集卡QT1138規(guī)格

l支持8通道同步采集,。16bit轉(zhuǎn)換精度,。

l模擬輸入帶寬120MHz

l采用250MSPS單芯片雙通道ADC。

l50歐姆AC耦合,,輸入滿幅度2Vpp,。支持DC藕合方式;支持高頻脈沖信號(hào)輸入,。

lPCIex8Gen2數(shù)據(jù)傳輸接口,,支持DMA傳輸,連續(xù)傳輸率2.8GB/s,。

lFPGA支持用戶自定義邏輯開(kāi)發(fā),。

l板載高穩(wěn)定度采集時(shí)鐘發(fā)生器,支持外時(shí)鐘和外觸發(fā)同步輸入,。

l輸入中頻:常用頻率為46MHz±10.23MHz

l輸入中頻信號(hào)功率:-60dBm~10dBm,;

l通道一致性:≤50ps。

1.2PCIEDA回放卡QT1238規(guī)格

l大支持8通道同步信號(hào)產(chǎn)生,,可配置

l16bit轉(zhuǎn)換精度,。

l高250MSPS數(shù)據(jù)更新率,可配置。

l板載高穩(wěn)定度采集時(shí)鐘發(fā)生器,,支持外時(shí)鐘和外觸發(fā)同步輸入,。

lPCIex8Gen2數(shù)據(jù)傳輸接口,支持DMA傳輸,,連續(xù)傳輸率2.6GB/s,。

l回放頻率經(jīng)上變頻可達(dá)1.3G/s,大于BDSB3的1268.52M,。

lFPGA支持用戶自定義邏輯開(kāi)發(fā),。

l模擬輸出重構(gòu)濾波器可配置,可以工作在,、第二以及第三奈奎斯特區(qū),。

l通道一致性:±3度

l鏈路增益:-40dB~-20dB;

l幅頻特性:

-3dB帶寬:≥20.46MHz,,

-40dB帶寬:≤50MHz,;

l帶外雜散抑制:≥40dBc;

l輸出本振泄露功率:≤-65dBm,;

l帶內(nèi)平坦度:≤±1.5dB,;

l輸出駐波:≤2.0。

1.3SSD固態(tài)盤

容量:4TBytes,;

存儲(chǔ)速率:≥1600MB/s(保證大采集速率下無(wú)丟數(shù))

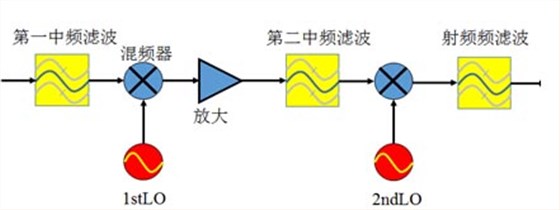

1.4上變頻模塊

可經(jīng)過(guò)上變頻到BDSB3的1268.52M,,LO:LocalOscillator本機(jī)振蕩器

二、系統(tǒng)情況

2.1采集/回放系統(tǒng):

2.2DA回放板系統(tǒng)結(jié)構(gòu)

采集回放卡包括如下特性:

1.8通道16bit250MSPS回放,,50歐姆直流/交流耦合,。2Vpp輸出。

2.低抖動(dòng),、低相噪時(shí)鐘發(fā)生器,,時(shí)鐘可設(shè)置。

3.支持外時(shí)鐘和外觸發(fā)接口,,可以多塊卡組成多通道同步工做模式,。

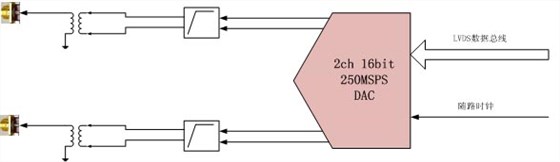

DAC輸出電路如上圖,重構(gòu)濾波器帶寬可以配置,。

2.3AD采集板系統(tǒng)結(jié)構(gòu)

采集卡包括如下特性:

1.8通道16bit250MSPS采集,,50歐姆交流耦合,支持2Vpp輸入,。

2.支持PCIE2.0x8接口,DMA傳輸速度2.8GB/s,。

3.低抖動(dòng)、低相噪時(shí)鐘發(fā)生器,,時(shí)鐘可設(shè)置,。

4.支持外時(shí)鐘和外觸發(fā)接口,,可以多塊卡組成多通道同步工做模式。

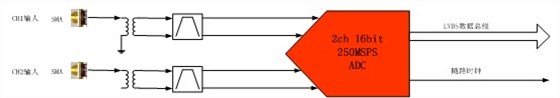

ADC輸入前端如上圖,,帶通濾波器中心頻率和帶寬可以配置,。

2.4采集/回放板外觀

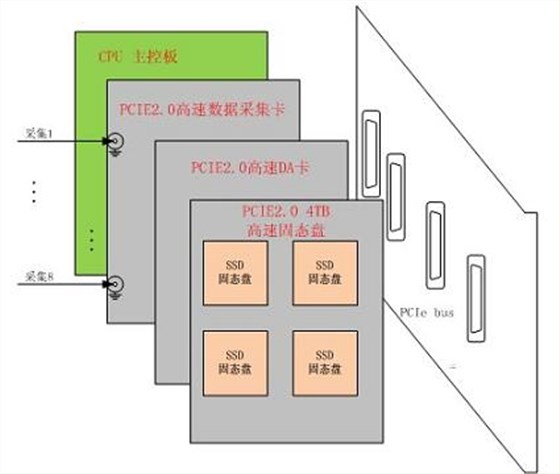

2.5高速存儲(chǔ)系統(tǒng)

該高速數(shù)據(jù)存儲(chǔ)卡采用PCIE2.0×8接口,板載4TB高速flash,。功耗待機(jī)14.5W,,讀寫(xiě)16W,板載四

SandForceSF-2582主控制器,,持續(xù)讀寫(xiě)速度高均為2.0GB/s,,隨機(jī)寫(xiě)入性

8KB160000IOPS,4KB2500000IOPS,,大IOPS260000,。支持TRIM/SCSIunmap

S.M.A.R.T.及企業(yè)級(jí)屬性,128/256-bitAES加密,,ECC錯(cuò)誤校驗(yàn),,支持掉電保護(hù)和數(shù)據(jù)寫(xiě)入保

(DataWriteAssurance)技術(shù)。

系統(tǒng)配套軟件

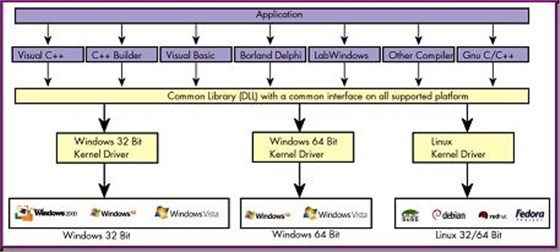

系統(tǒng)軟件包括應(yīng)用軟件,,二次開(kāi)發(fā)API函數(shù),,以及FPGA開(kāi)發(fā)環(huán)境三部分,。

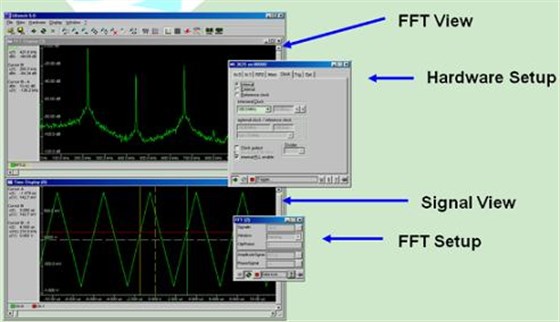

1.應(yīng)用軟件,,具有虛擬示波器功能,方便設(shè)置硬件,,讀取/保存數(shù)據(jù)以及波形顯示/頻譜分析功能,。

其功能和界面如下所示:

1.二次開(kāi)發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,支持C/C++,,labview的二次程序開(kāi)發(fā),。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳