中頻采集系統(tǒng)

采集系統(tǒng)規(guī)格:

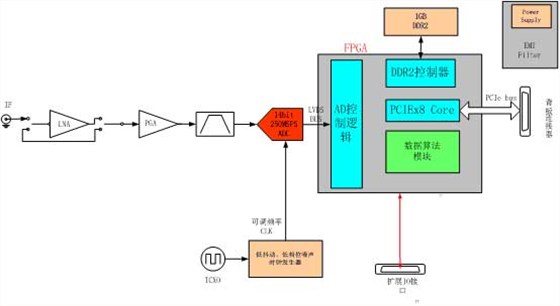

系統(tǒng)采用基于PCIEx8的FPGA開發(fā)系統(tǒng),包括如下幾個部分:

1.板載單通道14bit250MSPSADC,,采樣率可以通過軟件設(shè)置,。

2.低噪聲模擬前端,支持-50dBm到-20dBm的中頻信號輸入,。

3.程控增益放大器,,可以通過軟件設(shè)置增益。

4.板載1GBDDR2內(nèi)存,。

5.優(yōu)化的PCIexpressx8傳輸接口,,支持1200MB/s的連續(xù)傳輸速率。

6.高穩(wěn)定度,,超低低抖動時鐘發(fā)生器,。

7.低噪聲電源設(shè)計。

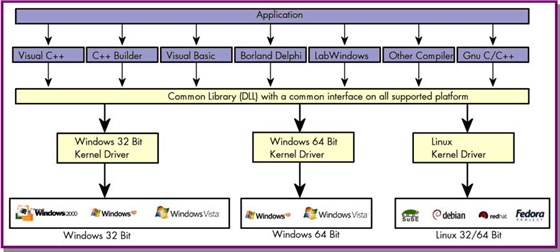

8.提供windows下的驅(qū)動程序以及API函數(shù),,SDK開發(fā)包,。

系統(tǒng)框圖如下:

系統(tǒng)功能描述:

1.采集通道支持250Msps采樣率,14bit,;

2.高速信號調(diào)理電路,,AC耦合,50歐姆/75歐姆阻抗匹配,。

3.放大器采用二級放大,,級低噪聲放大器采用固定20dB增益,可以旁通,。第二級為程控增益放大器,,范圍為-10dB到20dB可調(diào)。整體動態(tài)范圍為-10dB到40dB,。

4.帶通濾波器中心頻率為70MHz,,帶寬40MHz,,二階濾波器。

5.FPGA邏輯開放,,用戶可以自定義FPGA邏輯,。

6.支持FPGA實時計算FFT。我們采用的FPGA為XilinxXC5VSX95T具備的FFT能力如下:

16bit數(shù)據(jù)輸入,,32k點FFT,,工作時鐘250MHz,需要資源為,LUT3300個,,乘法單元9個,,延遲約400us。輸出數(shù)據(jù)的虛部和實部,。

二次開發(fā)API函數(shù):

我們提供豐富的接口函數(shù)和系統(tǒng)主要功能的例程,,支持C/C++,labview以及Matlab環(huán)境下的二次程序開發(fā),。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳