采集系統(tǒng)規(guī)格:

1、2通道,8bit,,5000MSPS ADC轉(zhuǎn)換器。

2,、信號(hào)調(diào)理模塊,支持PGA功能,。

3,、采用xilinxV6大規(guī)模FPGA。

4,、雙通道2*64bitDDR3

5,、低抖動(dòng)采集時(shí)鐘發(fā)生器。

6,、支持?jǐn)U展模塊,,可以擴(kuò)展PCIEx8,USB控制器以及RS232和RS422通信接口,。

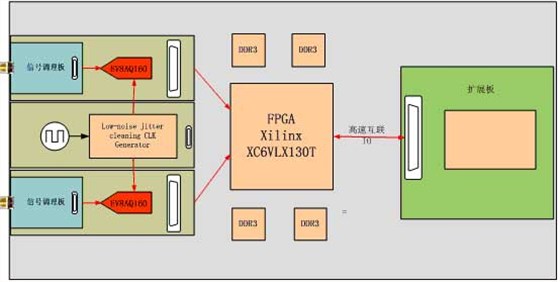

系統(tǒng)組成結(jié)構(gòu)如下:

該系統(tǒng)有以下組成部分:

1.主板包括:

xilinxXC6VLX130TFPGA以及配置電路

128bitDDR3內(nèi)存,,分上下64bit

擴(kuò)展接口,包括PCIEx8接口,,擴(kuò)展IO接口

FPGA電源模塊,,采用單5V輸入。

2.時(shí)鐘板包括:

晶體,。

PLL電路,,輸出兩路2.5GHZ時(shí)鐘。

時(shí)鐘電源,。

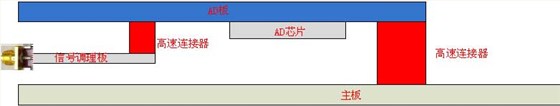

3.AD板包括:

E2V8bit/10bit5Gsps芯片,,本次采用8bit,但接口兼容10bit,。

ADC模擬電源

信號(hào)調(diào)理載板(AGC和PGA)

4.接口板包括:

接口控制芯片,,單片機(jī)。

RS422和RS232接口,。

信號(hào)調(diào)理板,,AD板以及主板的疊層關(guān)系如下:

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳