一,、 主要功能

中子測試項目邏輯設(shè)計概述如下:

(1)FPGA檢測(根據(jù)上位機的“開始檢測”指令(通過串口傳送))外部輸入的隨機序列,,隨機序列的低電平短時間為10ns。

(2)FPGA通過串口與計算機通訊,。當(dāng)接到計算機的“開始檢測”指令之后,,開始檢測輸入的隨機序列,,并將檢測結(jié)果以直方圖統(tǒng)計數(shù)據(jù)(見備注)的方式通過串口傳送給計算機。

(3) (在接到計算機的“開始檢測”指令后)當(dāng)隨機輸入序列的上升沿到來時,,FPGA要給出在以該上升沿的時間為時間節(jié)拍的256us時間窗內(nèi)隨機輸入序列的上升沿個數(shù),。

(4) (在接到計算機的“開始檢測”指令后)以隨機輸入序列的上升沿延時1ms處為時間點,FPGA給出在該時間點的256us時間窗隨機輸入序列的上升沿個數(shù),。

(5) 對兩組檢測結(jié)果(隨機輸入序列的上升沿和隨機輸入序列上升沿之后的1ms延時)進行統(tǒng)計,,統(tǒng)計出某個檢測結(jié)果(256us時間內(nèi)的隨機序列的上升沿個數(shù))的次數(shù)。

(6) 當(dāng)上位機發(fā)送“停止檢測”指令或是要求發(fā)送統(tǒng)計結(jié)果時,,FPGA見統(tǒng)計結(jié)果通過串口發(fā)送到計算機,。

備注:

關(guān)于檢測結(jié)果統(tǒng)計數(shù)據(jù)的解釋:

FPGA對輸入隨機序列的檢測結(jié)果為序列上升沿256us時間窗內(nèi)序列的上升沿個數(shù),為一個數(shù)值,。結(jié)果的數(shù)據(jù)統(tǒng)計就是統(tǒng)計同一技術(shù)結(jié)果出現(xiàn)的次數(shù),。(入檢測結(jié)果分別為3,3,2,2,1,1則統(tǒng)計結(jié)果為:出現(xiàn)1的次數(shù)為2,出現(xiàn)2的次數(shù)為2,,出現(xiàn)3的次數(shù)為2),。

二、 方案概述

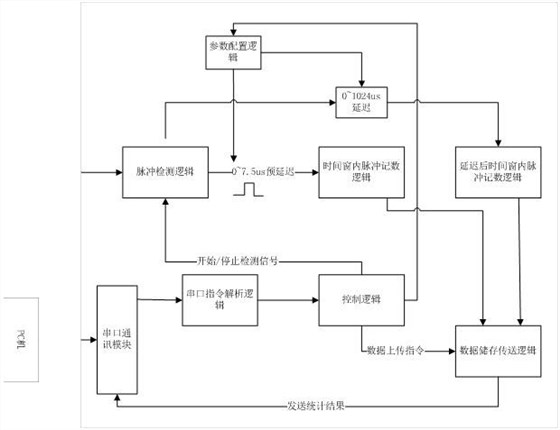

邏輯部分方案框圖如圖1所示,。

邏輯部分主要由上升沿檢測邏輯,、上升沿計數(shù)邏輯、PC指令解析邏輯,、系統(tǒng)運行邏輯(統(tǒng)計計數(shù)邏輯,、數(shù)據(jù)傳送邏輯、控制邏輯邏輯),、AD采集部分邏輯五部分組成,。隨機序列經(jīng)過上升沿檢測邏輯,輸出脈沖信號,。每有一個上升沿輸入,,上升沿檢測邏輯就輸出一個脈沖信號。上升沿檢測邏輯輸出的脈沖信號經(jīng)過上升沿計數(shù)邏輯對上升沿計數(shù),,計數(shù)結(jié)果為當(dāng)前時刻256us時間窗內(nèi)上升沿個數(shù),。PC指令解析邏輯對PC機的串口指令進行解析,將解析的指令送到控制邏輯,控制邏輯控制統(tǒng)計計數(shù)和數(shù)據(jù)傳送,。當(dāng)解析出開始檢測指令時,,控制邏輯根據(jù)兩個檢測點時刻(一個檢測點為隨機輸入序列的上升沿,另一個檢測點為上升沿延時1ms)使能鎖存器對上升沿計數(shù)器的計數(shù)結(jié)果進行鎖存,,并以該計數(shù)值為地址將對應(yīng)的統(tǒng)計計數(shù)器加1。當(dāng)解析停止檢測指令時控制邏輯禁能鎖存器和統(tǒng)計計數(shù)器,。當(dāng)解析清除指令時,,控制邏輯將統(tǒng)計計數(shù)器清零。當(dāng)解析傳送數(shù)據(jù)指令時,,控制邏輯將兩統(tǒng)計計數(shù)器的值分別傳送,,通過多路選擇器分別鎖存統(tǒng)計計數(shù)器結(jié)果,然后啟動串口發(fā)送邏輯發(fā)送鎖存器中的數(shù)值,。

后續(xù)將對上升沿計數(shù)邏輯,、控制邏輯進行概述。

三,、 脈沖計數(shù)邏輯

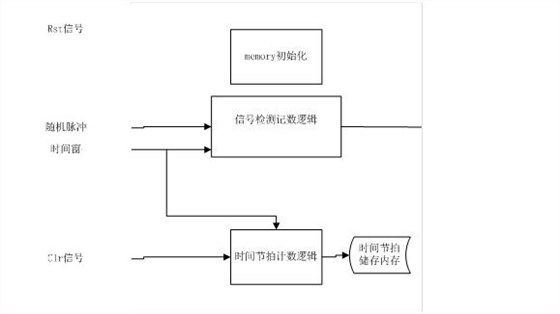

圖2脈沖檢測計數(shù)邏輯

上升沿計數(shù)邏輯主要由14bit計數(shù)器和脈沖時間節(jié)拍計數(shù)器組成,。CLK250M為系統(tǒng)時鐘(250Mhz/4ns),Rstn為系統(tǒng)復(fù)位信號,,低電平有效,。DI信號為上升沿檢測到的脈沖信號。輸入信號每有一個上升沿脈沖,,就輸出一個脈沖信號,,脈沖信號的脈寬為一個系統(tǒng)時鐘周期。DI信號同時輸入到14bit計數(shù)器和時間節(jié)拍計數(shù)器記錄此時刻,。14bit計數(shù)器和時間節(jié)拍計數(shù)器在系統(tǒng)復(fù)位時初始化為0,。計數(shù)器根據(jù)時間節(jié)拍計數(shù)器小值與當(dāng)前時間節(jié)拍差值與時間窗比較來決定計數(shù)器是加1、減1,、保持原值不變,。計數(shù)器操作情況如下:

當(dāng)CLK_D_value<=CLK_Window時計數(shù)器保持原值不變。

當(dāng)Pulse=1時,,計數(shù)器加1,。

當(dāng)CLK_D_value>CLK_Window時,計數(shù)器減1,時間節(jié)拍計數(shù)器加1,。

上升沿計數(shù)邏輯中計數(shù)器的計數(shù)值為256us時間段內(nèi)輸入隨機序列上升沿個數(shù),。

四、 系統(tǒng)控制邏輯

控制邏輯包括延遲控制邏輯和統(tǒng)計計數(shù)邏輯部分和統(tǒng)計數(shù)據(jù)傳送邏輯部分,。

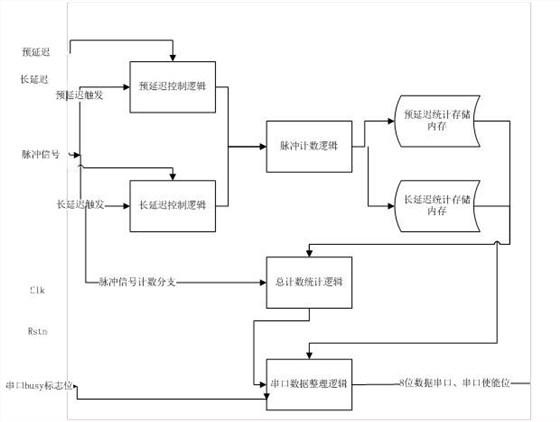

系統(tǒng)控制邏輯框圖如圖3所示,。

脈沖信號被延遲控制邏輯處理之后將相應(yīng)的觸發(fā)信號(處理后的脈沖信號)作為脈沖計數(shù)邏輯的觸發(fā)信號及將脈沖計數(shù)邏輯采集的時間窗內(nèi)脈沖個數(shù)存入相應(yīng)的內(nèi)存地址,其計數(shù)器連接在內(nèi)存模塊的地址總線上,,每觸發(fā)一次相應(yīng)地址上的計數(shù)器加1,。測量結(jié)束時,,將內(nèi)存中的數(shù)據(jù)傳送至串口數(shù)據(jù)整理邏輯,其會按照8位數(shù)據(jù)多次發(fā)送給串口控制模塊,,然后傳輸至PC機,。

總計數(shù)統(tǒng)計邏輯則是通過統(tǒng)計得到脈沖信號總計數(shù)和預(yù)延遲與長延遲的總計數(shù),然后傳輸?shù)酱跀?shù)據(jù)整理邏輯,,進行相應(yīng)處理,。

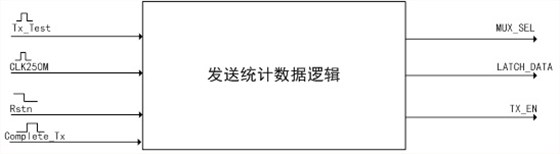

發(fā)送統(tǒng)計邏輯框圖如圖4所示。

信號說明:

Tx_Test信號為PC指令解析邏輯解析的傳送數(shù)據(jù)指令,,脈沖信號,,高電平有效。

Complete_Tx信號為串口發(fā)送邏輯返回的發(fā)送數(shù)據(jù)完成信號,。

當(dāng)檢測到Tx_Test為高電平時,,發(fā)送控制邏輯通過改變MUX_SEL的電平來分別將兩組統(tǒng)計計數(shù)器的結(jié)果鎖存,然后將發(fā)送邏輯的使能信號Tx_En拉高,,使能串口發(fā)送模塊,。

五、 總結(jié)

上述論述了邏輯設(shè)計部分的主要邏輯模塊,,其他邏輯模塊不在論述,。

為了我們共同的目標(biāo)“做專業(yè)的高速數(shù)據(jù)采集廠商”而共同努力!

關(guān)于坤馳科技:

坤馳科技是專注于高速數(shù)據(jù)采集與信號處理,、高速數(shù)據(jù)存儲與記錄的高科技公司,。坤馳科技為用戶提供成熟的標(biāo)準(zhǔn)高速數(shù)據(jù)采集產(chǎn)品與技術(shù),也可為用戶提供定制化的高速信號采集解決方案,。目前坤馳科技服務(wù)過的研究所,、科研單位已達近百家。高速數(shù)據(jù)采集產(chǎn)品線涵蓋PCIExpress,、cPCI,、PXIe、VPX,、USB等總線,,包含高速AD、DA平臺,、FPGA,、DSP處理平臺,SATA/SSD,、Flash存儲平臺等,。

全國咨詢電話:400-000-4026

公司官方網(wǎng)站:http://jtyykv.cn

官方微博:http://e.weibo.com/queentest

官方微信:queentest或掃描:

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳